S2042

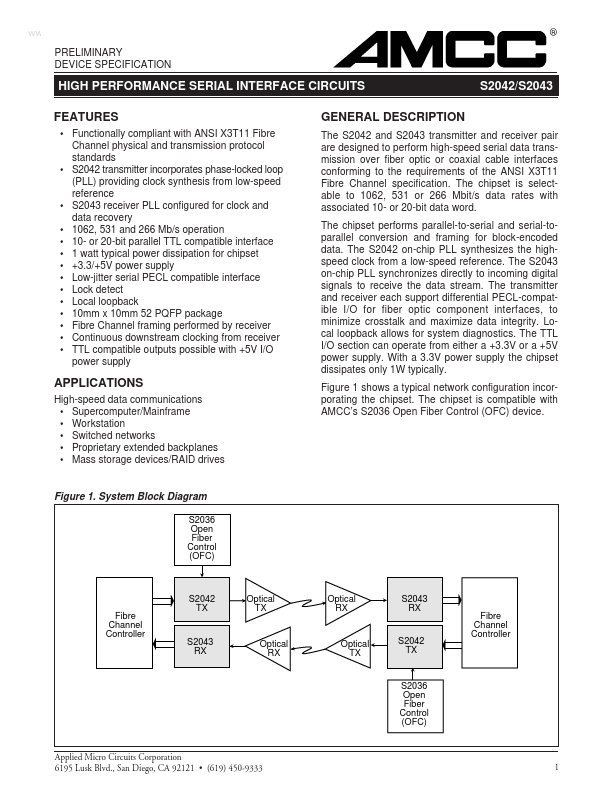

Overview

- Functionally compliant with ANSI X3T11 Fibre Channel physical and transmission protocol standards

- S2042 transmitter incorporates phase-locked loop (PLL) providing clock synthesis from low-speed reference

- S2043 receiver PLL configured for clock and data recovery

- 1062, 531 and 266 Mb/s operation

- 10- or 20-bit parallel TTL compatible interface

- 1 watt typical power dissipation for chipset

- +3.3/+5V power supply

- Low-jitter serial PECL compatible interface

- Lock detect

- Local loopback