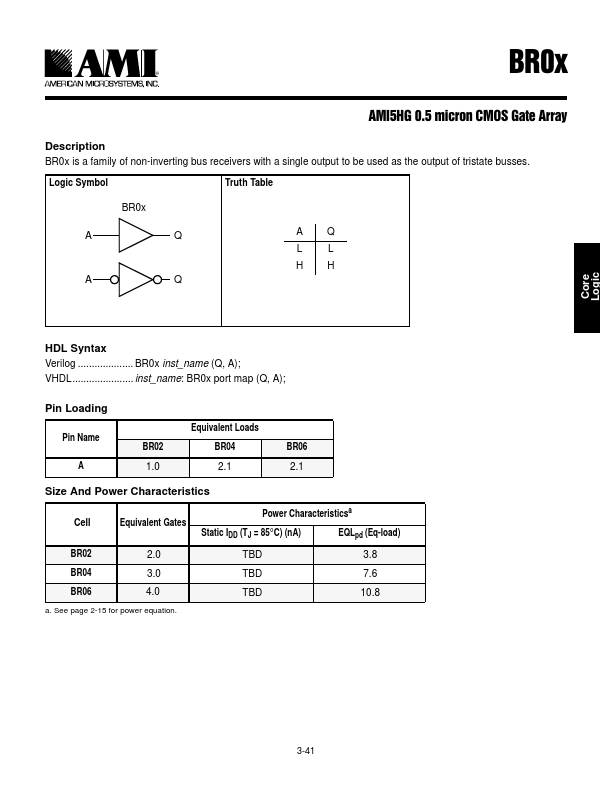

- Part: BR02

- Description: CMOS Gate Array

- Manufacturer: AMI

- Size: 23.79 KB

Datasheets by Manufacturer

| Part Number | Manufacturer | Description |

|---|---|---|

| LXHL-BR02 | luxeon | Luxeon Emitter |

| M4Z28-BR00SH | STMicroelectronics | 5V or 3V NVRAM SUPERVISOR FOR LPSRAM |

| M4Z32-BR00SH | STMicroelectronics | 5V or 3V NVRAM SUPERVISOR FOR LPSRAM |

| M4Z32-BR00SH1 | STMicroelectronics | ZEROPOWER SNAPHAT Battery |

| M4ZXX-BR00SH | STMicroelectronics | ZEROPOWER SNAPHAT Battery |

| M4Z28-BR00SH | STMicroelectronics | ZEROPOWER SNAPHAT Battery |

| M4Z28-BR00SH1 | STMicroelectronics | ZEROPOWER SNAPHAT Battery |

| M4Z28-BR00SH6 | STMicroelectronics | ZEROPOWER SNAPHAT Battery |

| M4Z32-BR00SH | STMicroelectronics | 5V or 3V NVRAM SUPERVISOR FOR LPSRAM |

| M4Z32-BR00SH | STMicroelectronics | ZEROPOWER SNAPHAT Battery |