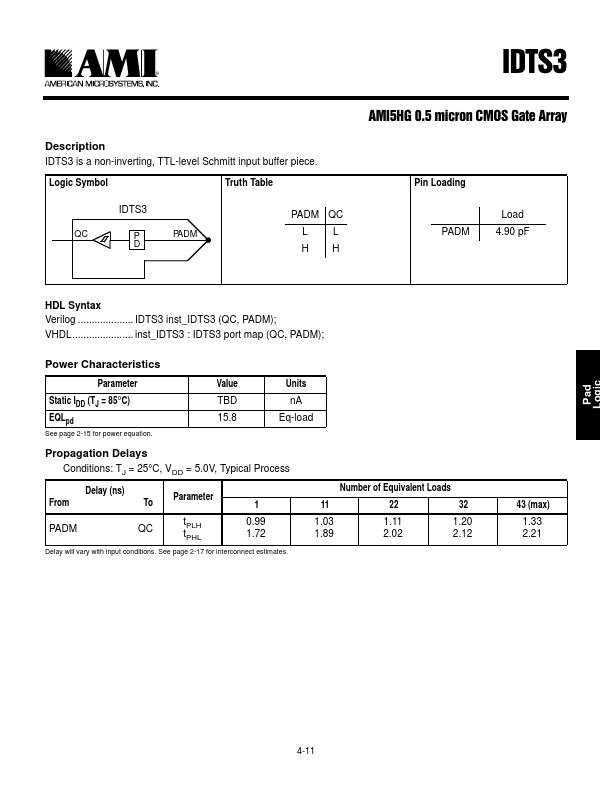

- Part: IDTS3

- Description: CMOS Gate Array

- Manufacturer: AMI

- Size: 17.39 KB

Datasheets by Manufacturer

| Part Number | Manufacturer | Description |

|---|---|---|

| QS3257 | IDT | HIGH-SPEED CMOS QUICKSWITCH QUAD 2:1 MUX/DEMUX |

| 8413S12B | IDT | HCSL/ LVCMOS Clock Generator |

| IDT74AHCT245 | IDT | High Speed CMOS Non-Inverting Buffer Transceiver |

| IDT74AHCT273 | IDT | High Speed CMOS Octal D Flip-Flop |

| IDT54AHCT299 | IDT | High Speed CMOS 8-Input Universal Shift Register |

| IDT74AHCT299 | IDT | High Speed CMOS 8-Input Universal Shift Register |

| IDT54AHCT373 | IDT | High Speed CMOS Octal Transparent Latch |

| IDT74AHCT373 | IDT | High Speed CMOS Octal Transparent Latch |

| IDT54AHCT374 | IDT | High Speed CMOS Octal D Register |

| IDT74AHCT244 | IDT | High Speed CMOS Octal Buffer/Line Driver |