AMIS-710650-A6

AMIS-710650-A6 is CIS Module manufactured by AMI SEMICONDUCTOR.

AMIS-710650-A6: Color CIS Module

Analog Video Output

Data Sheet

1.0 Description

The AMIS-710650-A6 (PI650MC-A6C) is a color contact image sensor (CIS) module. The module contains seven image sensor chips, AMIS-720058 (PI6058H), a product of AMI Semiconductor. These chips are sequentially cascaded to provide a line array of photodetectors. Each photo-detector in the image sensor possesses its own independent processing circuit. As the photo-sensors’ digital shift register scans the image sensor chip, it sequentially produces the video signals at the output of the image array. The AMIS710650-A6’s mechanical outline drawing is shown in Figure 6.

2.0 Key Features

- -

- -

- -

- -

- - 600 and 300dpi selectable resolutions 23.6dpm and 11.8dpm, 102mm scanning length 344 or 172 image sensor elements (pixels) Low power-single power supply at 3.3V Light source, lens and sensor are integrated into a single module High speed page scan

- up to 602µsec/line @ 4MHz pixel rate Analog output RGB color LED light source pact size ≅ 12.3mm x 18.9mm x 125mm Light weight

3.0 Overview

The AMIS-710650-A6 has a 102mm read width. Its minimum line rate is 602us/line with a maximum clock pulse (CP) equal to 4.0MHz (pixel rate (PRATE), of 4.0MHz). Unless stated otherwise, all data was taken with CP = 3.0MHz (PRATE = 3.0MHz) and an integration time of 685us/line. The sensor photo-site density is 23.64elements/mm. The module has one analog video output, two clock inputs, clock and start pulse (CP and SP), one reference voltage input for the amplifier output bias level control, one power supply input and four LED inputs.

..

4.0 Scan Overview

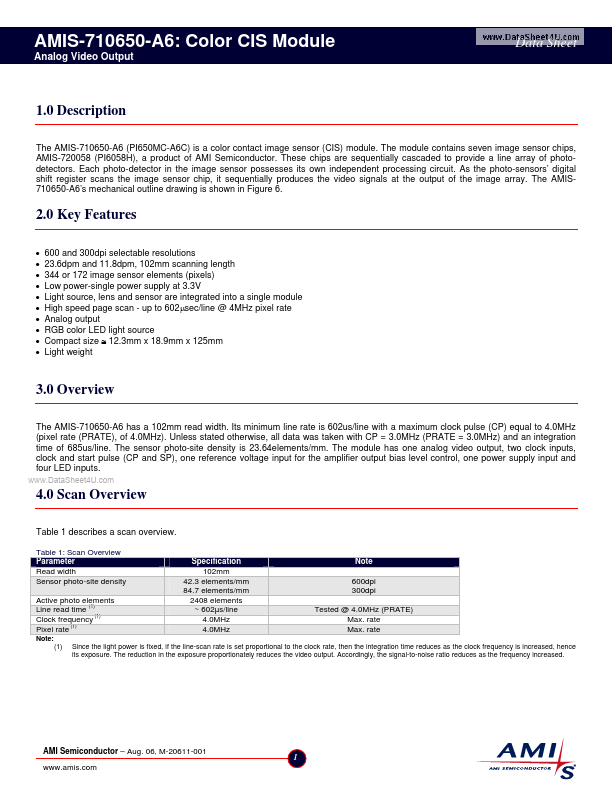

Table 1 describes a scan overview.

Table 1: Scan Overview Parameter Read width Sensor photo-site density Active photo elements (1) Line read time (1) Clock frequency (1) Pixel rate

Note: (1) Since the light power is fixed, if the line-scan rate is set proportional to the clock rate, then the integration time reduces as the clock...