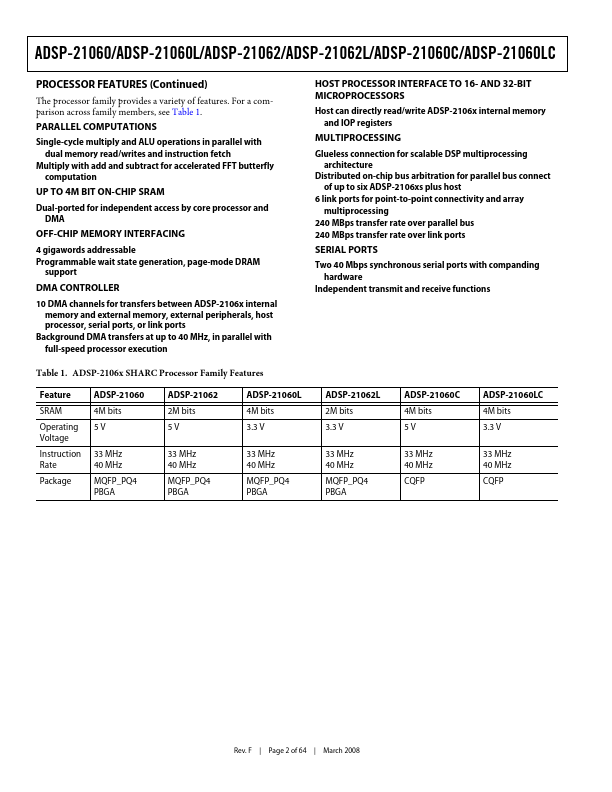

ADSP-21062 Description

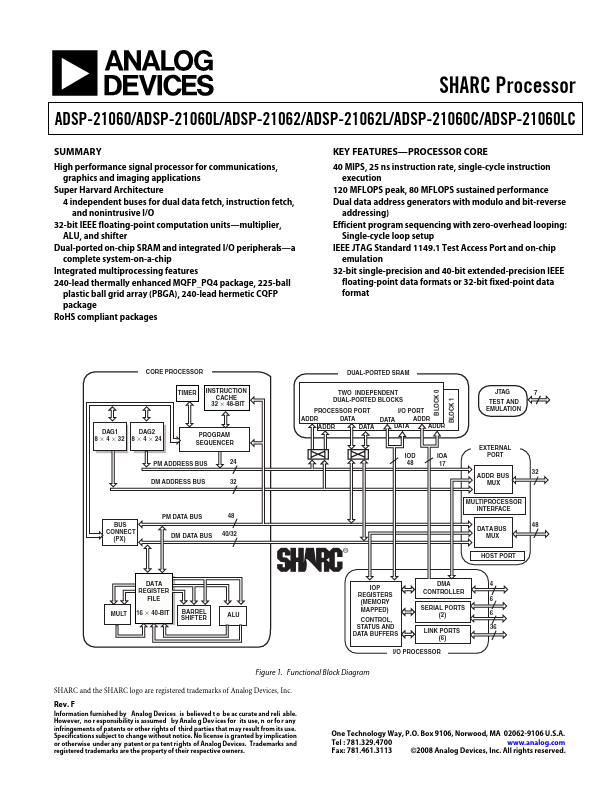

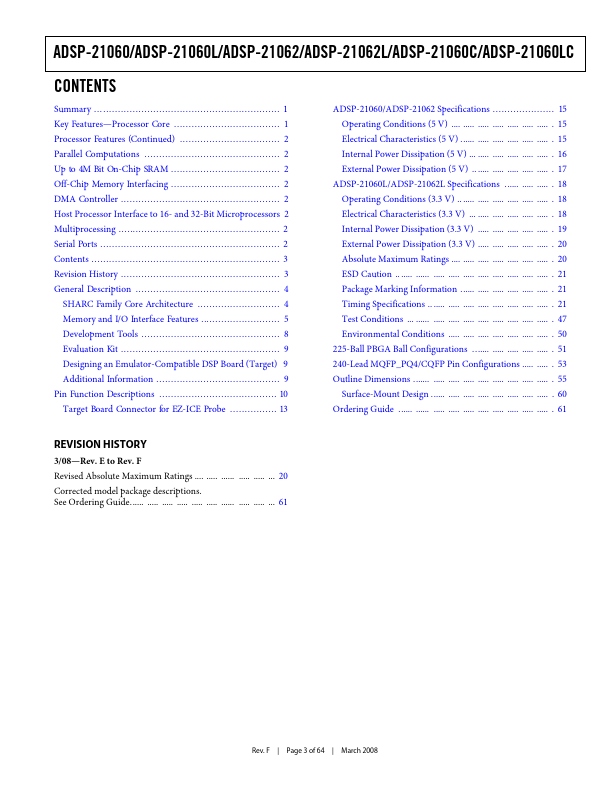

SHARC Processor ADSP-21060/ADSP-21060L/ADSP-21062/ADSP-21062L/ADSP-21060C/ADSP-21060LC SUMMARY High performance signal processor for munications, graphics and imaging applications Super Harvard Architecture 4 independent buses for dual data fetch, instruction fetch, and nonintrusive I/O 32-bit IEEE floating-point putation units multiplier, ALU, and shifter Dual-ported on-chip SRAM and integrated I/O peripherals a...