ATF1508RE Overview

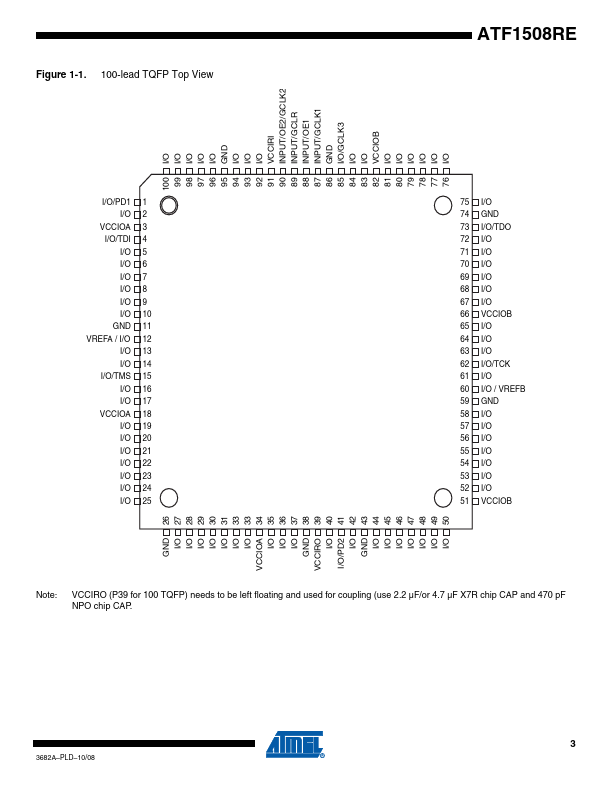

The ATF1508RE is a high-performance, high-density plex programmable logic device (CPLD) that utilizes Atmel’s proven electrically-erasable memory technology. With 128 logic macrocells and up to 84 inputs, it easily integrates logic from several TTL, SSI, MSI, LSI and classic PLDs. The ATF1508RE’s enhanced routing switch matrices increase usable gate count and the odds of successful pin-locked design modifications.

ATF1508RE Key Features

- High-density, High-performance Fully CMOS, Electrically-erasable plex Programmable Logic Device

- 128 Macrocells

- 5.0 ns Pin-to-pin Propagation Delay

- Registered Operation up to 333 MHz

- Enhanced Routing Resources

- Optimized for 3.3V Operation

- On-chip Voltage Regulator

- 2 I/O Banks to Facilitate Multi-voltage I/O Operation: 1.5V, 1.8V, 2.5V, 3.3V

- SSTL2 and SSTL3 I/O Standards

- In-System Programming (ISP) Supported