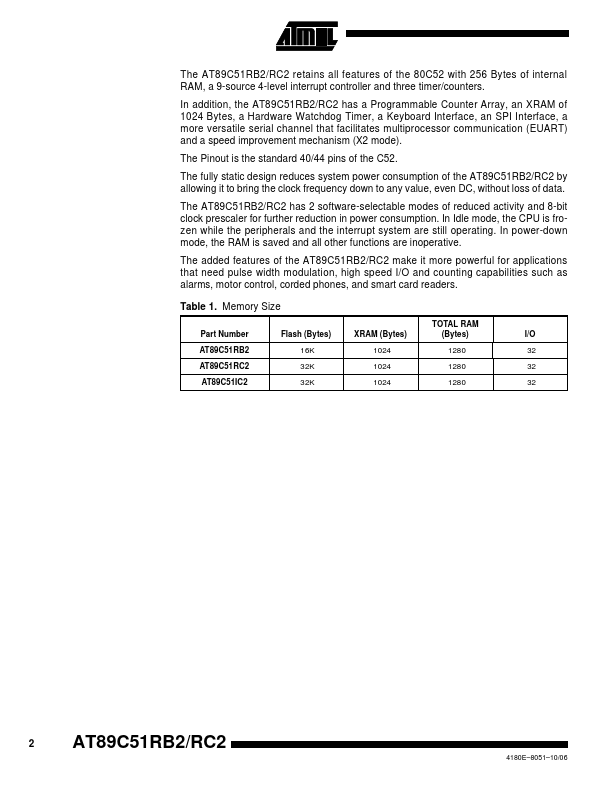

Datasheet Summary

Features

- 80C52 patible

- 8051 Pin and Instruction patible

- Four 8-bit I/O Ports

- Three 16-bit Timer/Counters

- 256 Bytes Scratch Pad RAM

- 9 Interrupt Sources with 4 Priority Levels

- Dual Data Pointer

- Variable Length MOVX for Slow RAM/Peripherals

- ISP (In-system Programming) Using Standard VCC Power Supply

- Boot ROM Contains Low Level Flash Programming Routines and a Default Serial

Loader

- High-speed Architecture

- In Standard Mode: 40 MHz (Vcc 2.7V to 5.5V, both Internal and external code execution) 60 MHz (Vcc 4.5V to 5.5V and Internal Code execution only)

- In X2 mode (6 Clocks/machine cycle) 20 MHz (Vcc 2.7V to 5.5V, both Internal and external code execution) 30 MHz...