RTAX2000SL Overview

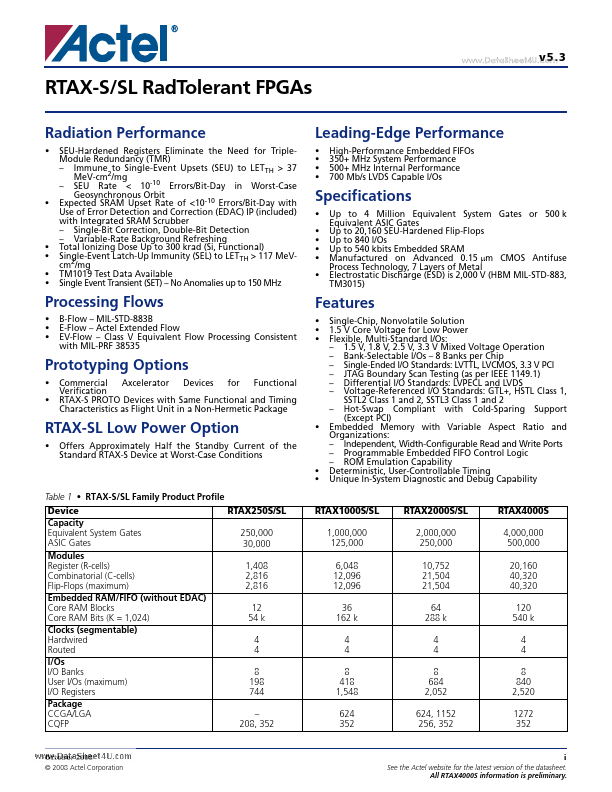

v5.3 .. RTAX-S/SL RadTolerant FPGAs Radiation Performance SEU-Hardened Registers Eliminate the Need for TripleModule Redundancy (TMR) Immune to Single-Event Upsets (SEU) to LETTH > 37 MeV-cm2/mg SEU Rate < 10-10 Errors/Bit-Day in Worst-Case Geosynchronous.

RTAX2000SL Key Features

- Single-Chip, Nonvolatile Solution 1.5 V Core Voltage for Low Power Flexible, Multi-Standard I/Os

- 1.5 V, 1.8 V, 2.5 V, 3.3 V Mixed Voltage Operation

- Bank-Selectable I/Os

- 8 Banks per Chip

- Single-Ended I/O Standards: LVTTL, LVCMOS, 3.3 V PCI

- JTAG Boundary Scan Testing (as per IEEE 1149.1)

- Differential I/O Standards: LVPECL and LVDS

- Voltage-Referenced I/O Standards: GTL+, HSTL Class 1, SSTL2 Class 1 and 2, SSTL3 Class 1 and 2

- Hot-Swap pliant with Cold-Sparing Support (Except PCI) Embedded Memory with Variable Aspect Ratio and Organizations

- Independent, Width-Configurable Read and Write Ports