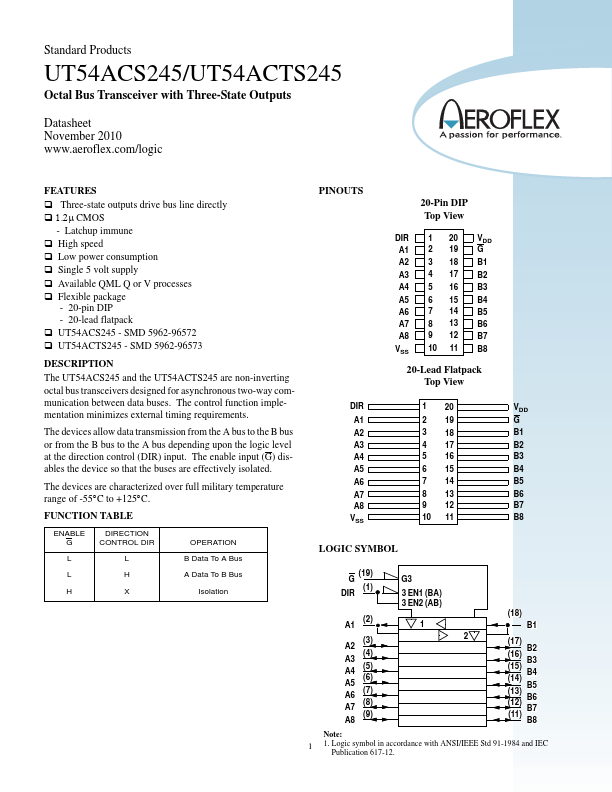

UT54ACTS245 Description

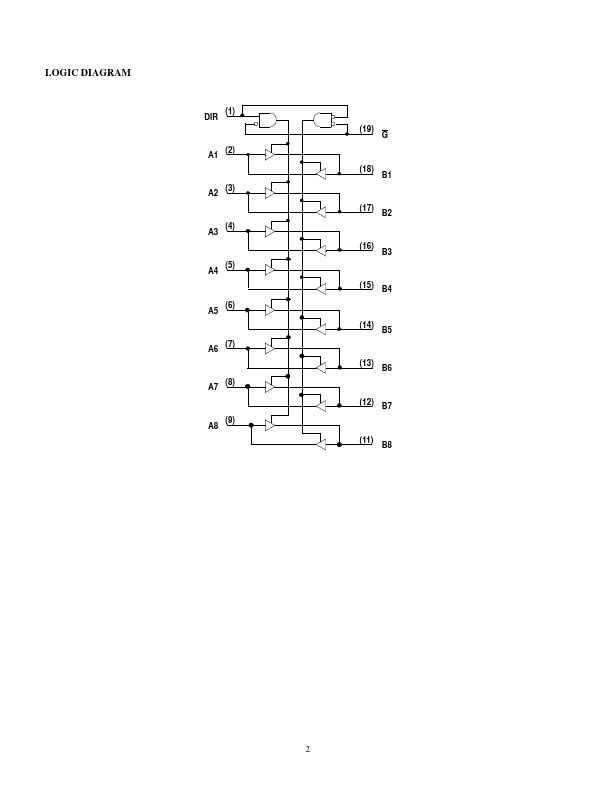

The UT54ACS245 and the UT54ACTS245 are non-inverting octal bus transceivers designed for asynchronous two-way munication between data buses. The control function implementation minimizes external timing requirements. The devices allow data transmission from the A bus to the B bus or from the B bus to the A bus depending upon the logic level at the direction control (DIR) input.

UT54ACTS245 Key Features

- Latchup immune High speed Low power consumption Single 5 volt supply Available QML Q or V processes Flexible p

- 20-pin DIP

- 20-lead flatpack UT54ACS245

- SMD 5962-96572 UT54ACTS245

- SMD 5962-96573