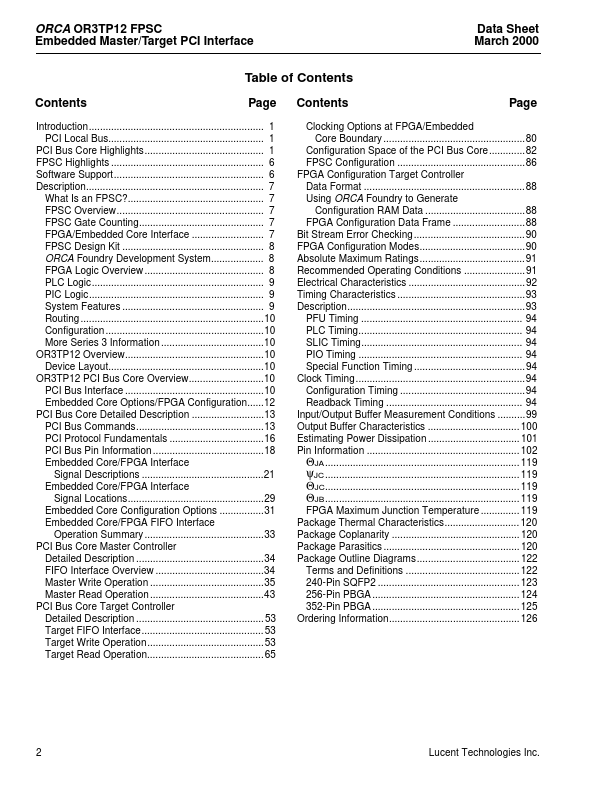

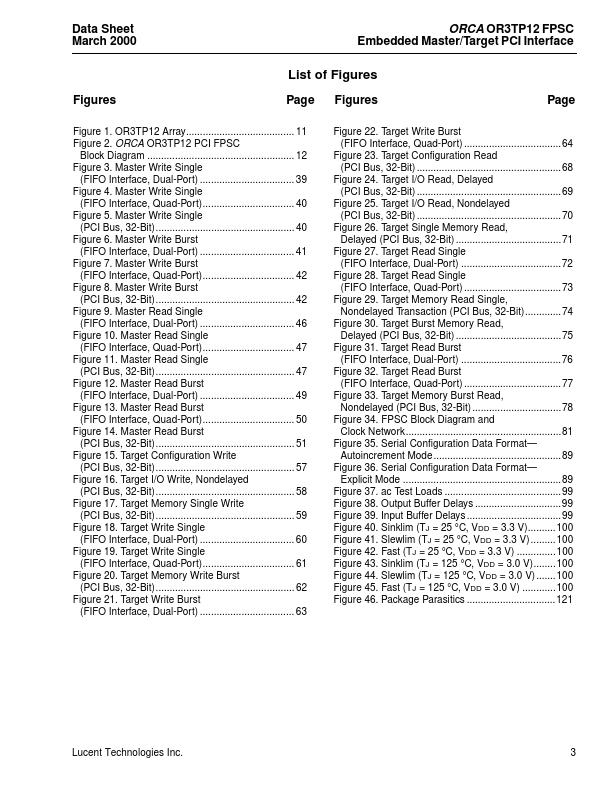

Datasheet Summary

Data Sheet March 2000

ORCA® OR3TP12 Field-Programmable System Chip (FPSC) Embedded Master/Target PCI Interface

Introduction

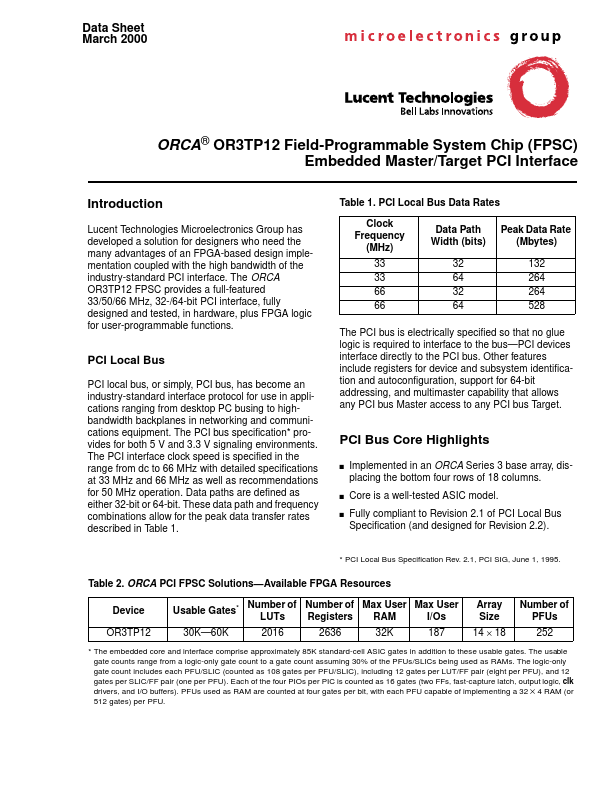

Lucent Technologies Microelectronics Group has developed a solution for designers who need the many advantages of an FPGA-based design implementation coupled with the high bandwidth of the industry-standard PCI interface. The ORCA OR3TP12 FPSC provides a full-featured 33/50/66 MHz, 32-/64-bit PCI interface, fully designed and tested, in hardware, plus FPGA logic for user-programmable functions. Table 1. PCI Local Bus Data Rates Clock Frequency (MHz) 33 33 66 66 Data Path Width (bits) 32 64 32 64 Peak Data Rate (Mbytes) 132 264 264 528

PCI Local Bus

PCI local bus, or...