AS4LC4M4F1

Key Features

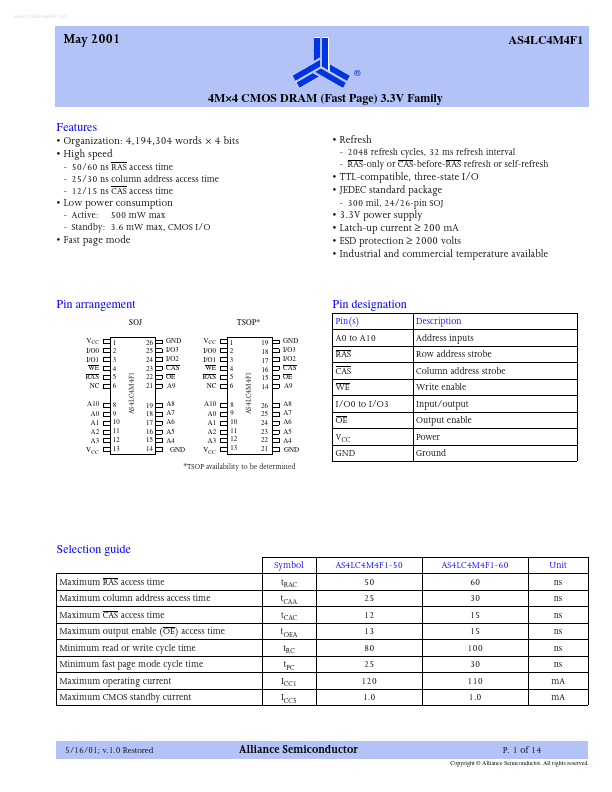

- Organization: 4,194,304 words × 4 bits

- High speed - 50/60 ns RAS access time - 25/30 ns column address access time - 12/15 ns CAS access time

- Refresh - 2048 refresh cycles, 32 ms refresh interval - RAS-only or CAS-before-RAS refresh or self-refresh

- TTL-compatible, three-state I/O

- JEDEC standard package - 300 mil, 24/26-pin SOJ

- Low power consumption - Active: 500 mW max - Standby: 3.6 mW max, CMOS I/O

- Fast page mode

- 3.3V power supply

- Latch-up current ≥ 200 mA

- ESD protection ≥ 2000 volts