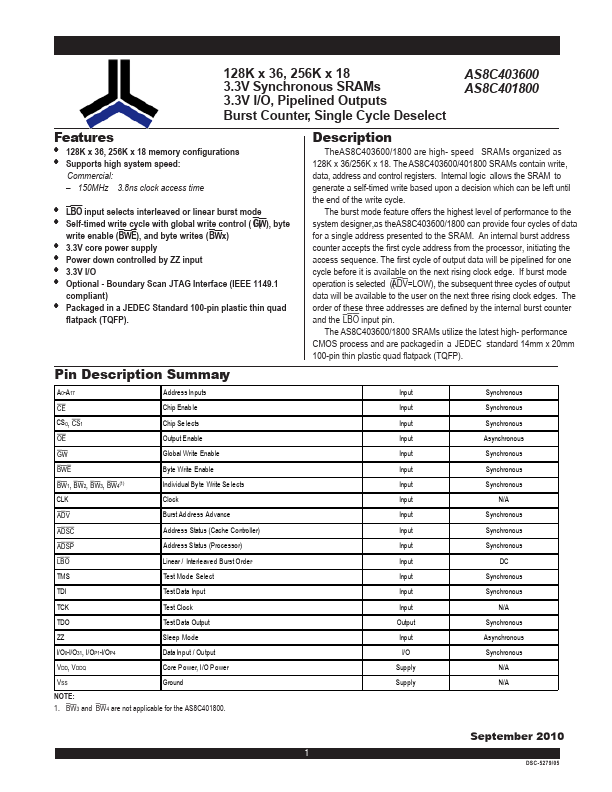

AS8C401800 Description

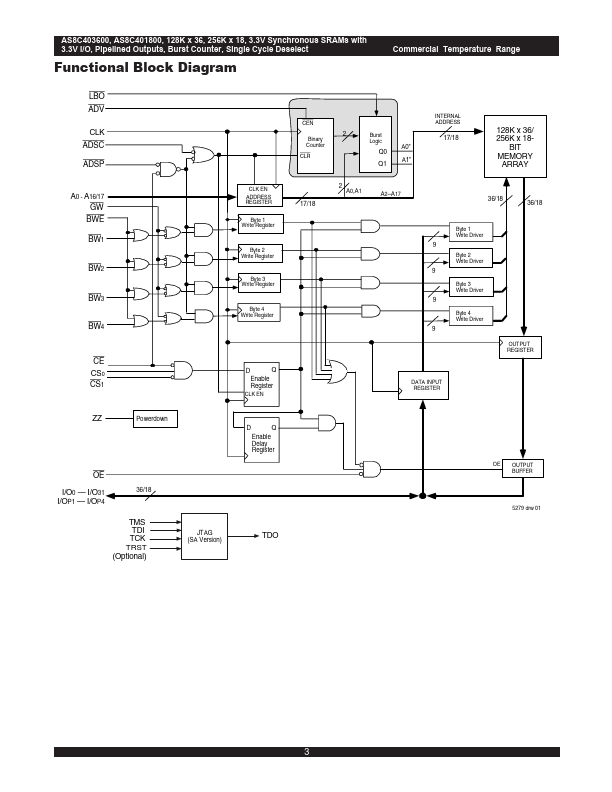

TheAS8C403600/1800 are high- speed SRAMs organized as 128K x 36/256K x 18. The AS8C403600/401800 SRAMs contain write, data, address and control registers. Internal logic allows the SRAM to generate a self-timed write based upon a decision which can be left until the end of the write cycle.

AS8C401800 Key Features

- 150MHz 3.8ns clock access time LBO input selects interleaved or linear burst mode Self-timed write cycle with global wri

- Boundary Scan JTAG Interface (IEEE 1149.1 pliant) Packaged in a JEDEC Standard 100-pin plastic thin quad flatpack (TQFP)