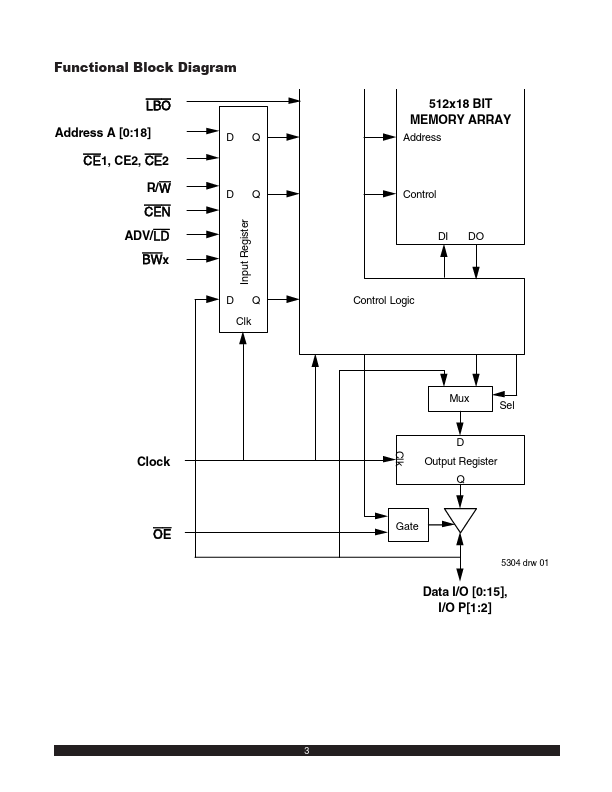

AS8C801801 Description

They are designed to eliminate dead bus pin thin plastic quad flatpack (TQFP) . cycles when turning the bus around between reads and writes, or writes and TM reads. Thus, they have been given the name ZBT , or Zero Bus Turnaround.