Datasheet Summary

..

July 2004

JTAG Test Controller

Description

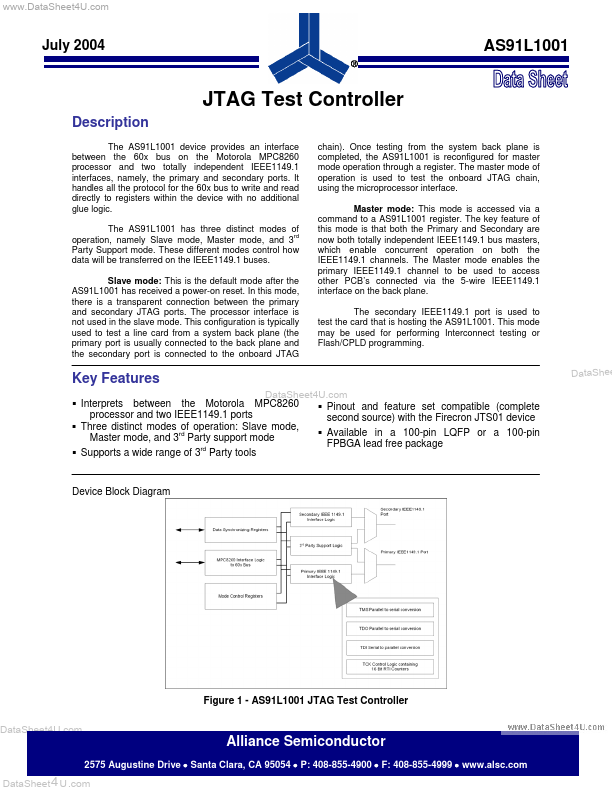

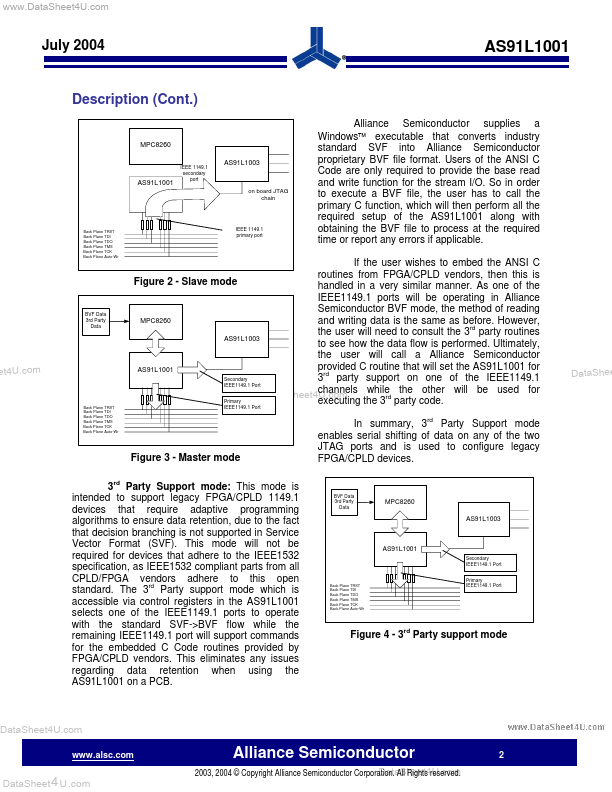

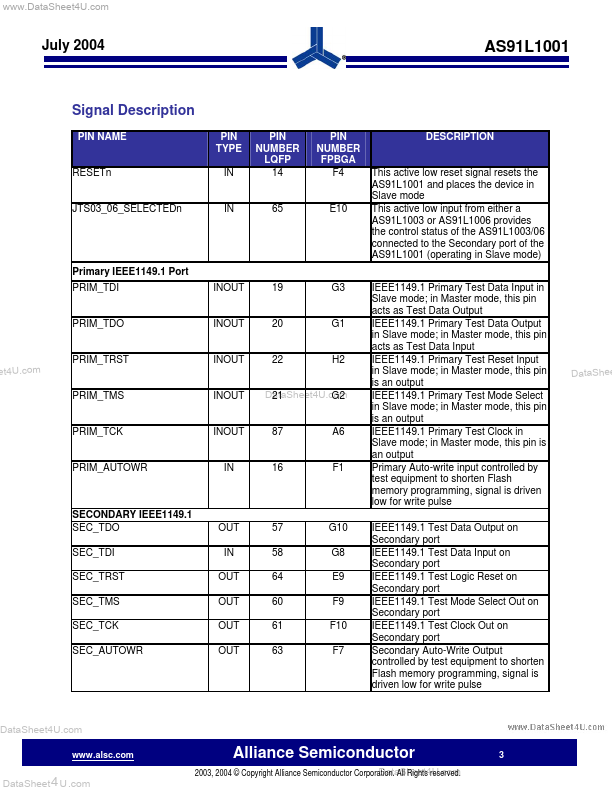

The AS91L1001 device provides an interface between the 60x bus on the Motorola MPC8260 processor and two totally independent IEEE1149.1 interfaces, namely, the primary and secondary ports. It handles all the protocol for the 60x bus to write and read directly to registers within the device with no additional glue logic. The AS91L1001 has three distinct modes of rd operation, namely Slave mode, Master mode, and 3 Party Support mode. These different modes control how data will be transferred on the IEEE1149.1 buses. Slave mode: This is the default mode after the AS91L1001 has received a power-on reset. In this mode,...