AS7C34096A

AS7C34096A is 3.3V 512K x 8 CMOS SRAM manufactured by Alliance Semiconductor Corporation.

February 2004 e e hAS7C34096

- Pin patible to S

- Industrial and mercial temperature a 524,288 words × 8 bits t

- Organization: a and ground pins

- Center power D .speed

- High w w w- Low power consumption: ACTIVE

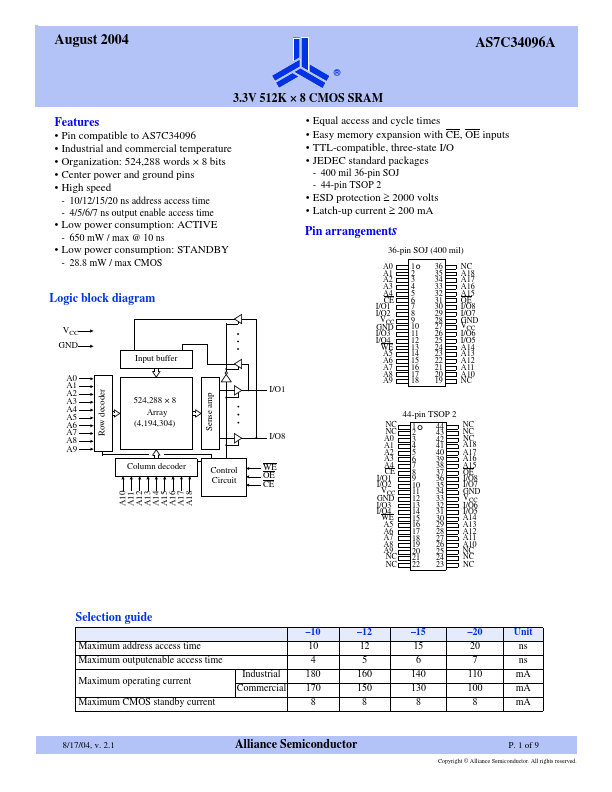

Features

- 10/12/15/20 ns address access time

- 4/5/6/7 ns output enable access time

- 650 mW / max @ 10 ns

- 18 mW / max CMOS

U 4 t

.c om

®

3.3V 512K × 8 CMOS SRAM

- Equal access and cycle times

- Easy memory expansion with CE, OE inputs

- TTL-patible, three-state I/O

- JEDEC standard packages

- 400 mil 36-pin SOJ

- 44-pin TSOP 2

- 48 pin BGA. 6 X 9mm

Pin arrangements

A0 A1 A2 A3 A4 CE I/O1 I/O2 VCC GND I/O3 I/O4 WE A5 A6 A7 A8 A9 1 2 3 4 5 6 7 8 9 10...