EP1S25 Overview

Key Specifications

Package: BGA

Mount Type: Surface Mount

Pins: 780

Operating Voltage: 1.5 V

Key Features

- Introduction Chapter

- Stratix Architecture Chapter

- Configuration & Testing Chapter

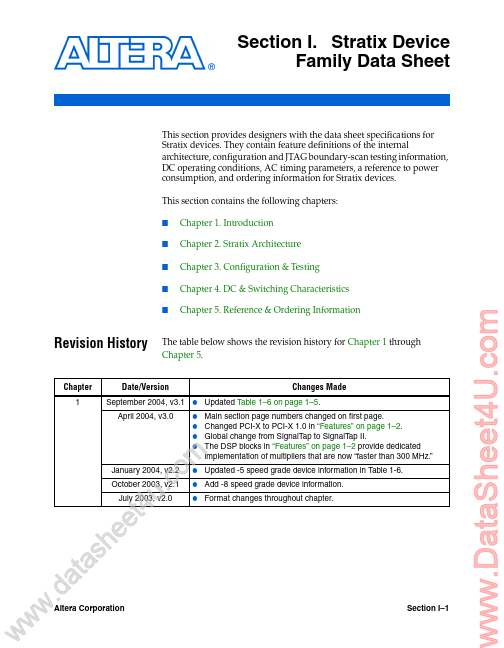

- DC & Switching Characteristics Revision History Chapter 1 The table below shows the revision history for Chapter 1 through Chapter

- Altera Corporation Section I–1 Preliminary Chapter