EPM3256A

Overview

PCI compatible Bus-friendly architecture including programmable slew-rate control Open-drain output option Programmable mac.

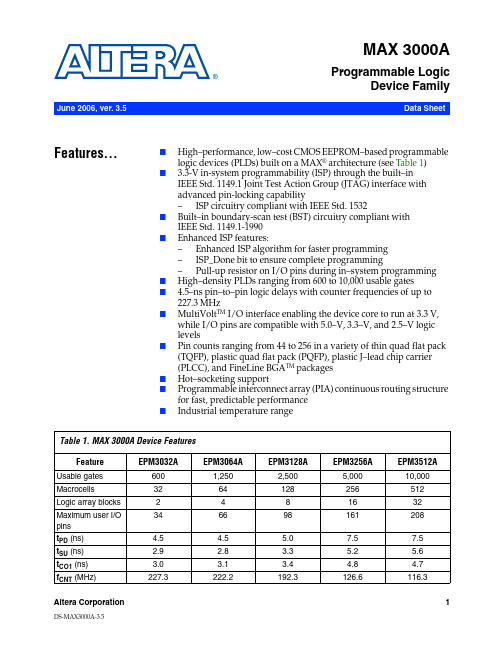

- High-performance, low-cost CMOS EEPROM-based programmable logic devices (PLDs) built on a MAX® architecture (see Table 1)

- 3.3-V in-system programmability (ISP) through the built-in IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface with advanced pin-locking capability - ISP circuitry compliant with IEEE Std. 1532

- Built-in boundary-scan test (BST) circuitry compliant with IEEE Std. 1149.1-1990

- Enhanced ISP features: - Enhanced ISP algorithm for faster programming - ISP_Done bit to ensure complete programming - Pull-up resistor on I/O pins during in-system programming

- High-density PLDs ranging from 600 to 10,000 usable gates

- 4.5-ns pin-to-pin logic delays with counter frequencies of up to

- 3 MHz

- MultiVoltTM I/O interface enabling the device core to run at 3.3 V, while I/O pins are compatible with 5.0-V, 3.3-V, and 2.5-V logic levels

- Pin counts ranging from 44 to 256 in a variety of thin quad flat pack (TQFP), plastic quad flat pack (PQFP), plastic J-lead chip carrier (PLCC), and FineLine BGATM packages

- Hot-socketing support