EPM7128E

Key Features

- High-performance, EEPROM-based programmable logic devices (PLDs) based on second-generation MAX® architecture

- 5.0-V in-system programmability (ISP) through the built-in IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface available in MAX 7000S devices - ISP circuitry compatible with IEEE Std. 1532

- Includes 5.0-V MAX 7000 devices and 5.0-V ISP-based MAX 7000S devices

- Built-in JTAG boundary-scan test (BST) circuitry in MAX 7000S devices with 128 or more macrocells

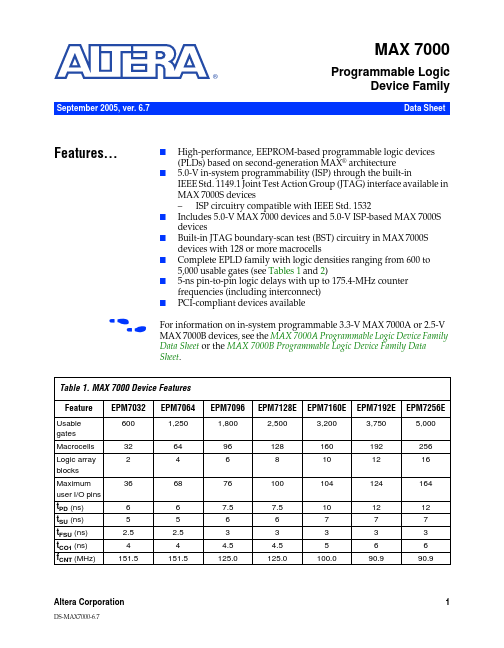

- Complete EPLD family with logic densities ranging from 600 to 5,000 usable gates (see Tables 1 and 2)

- 5-ns pin-to-pin logic delays with up to 175.4-MHz counter frequencies (including interconnect)

- PCI-compliant devices available For information on in-system programmable 3.3-V MAX 7000A or 2.5-V MAX 7000B devices, see the MAX 7000A Programmable Logic Device Family Data Sheet or the MAX 7000B Programmable Logic Device Family Data Sheet. Table

- MAX 7000 Device Features Feature EPM7032 Usable gates Macrocells Logic array blocks Maximum user I/O pins tPD (ns) tSU (ns) tFSU (ns) tCO1 (ns) fCNT (MHz) 600 32 2 36 6 5 2.5 4 151.5 EPM7064 1,250 64 4 68 6 5 2.5 4 151.5