EPM7160E Overview

Key Specifications

Package: QFP

Mount Type: Surface Mount

Pins: 160

Operating Voltage: 5 V

Key Features

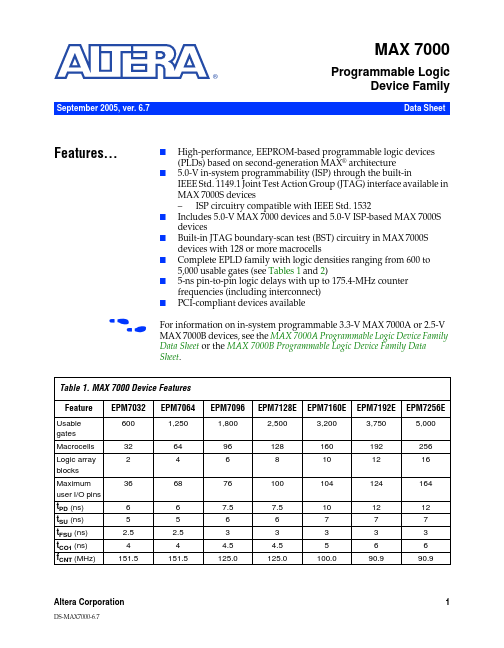

- High-performance, EEPROM-based programmable logic devices (PLDs) based on second-generation MAX® architecture

- 5.0-V in-system programmability (ISP) through the built-in IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface available in MAX 7000S devices