EPC2 Key Features

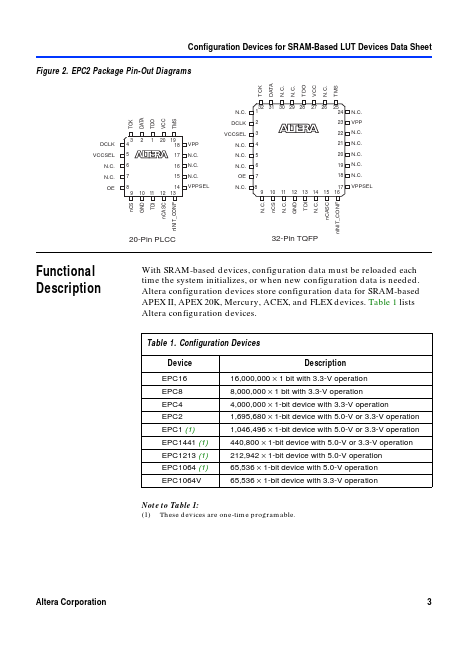

- 8-pin plastic dual in-line package (PDIP)

- 20-pin plastic J-lead chip carrier (PLCC) package

- 32-pin plastic thin quad flat pack (TQFP) package

- 100-pin plastic thin quad flat pack (TQPF) package

- 88-pin Ultra FineLine BGATM package EPC2 device has reprogrammable Flash configuration memory

- 5.0-V and 3.3-V in-system programmability (ISP) through the built-in IEEE Std. 1149.1 Joint Test Action Group (JTAG) int

- Built-in JTAG boundary-scan test (BST) circuitry pliant with IEEE Std. 1149.1

- ISP circuitry is patible with IEEE Std. 1532 for EPC2 configuration device

- Supports programming through Serial Vector Format Files (.svf), JamTM Standard Test and Programming Language (STAPL) Fil

- nINIT_CONF pin allows a JTAG instruction to initiate device configuration