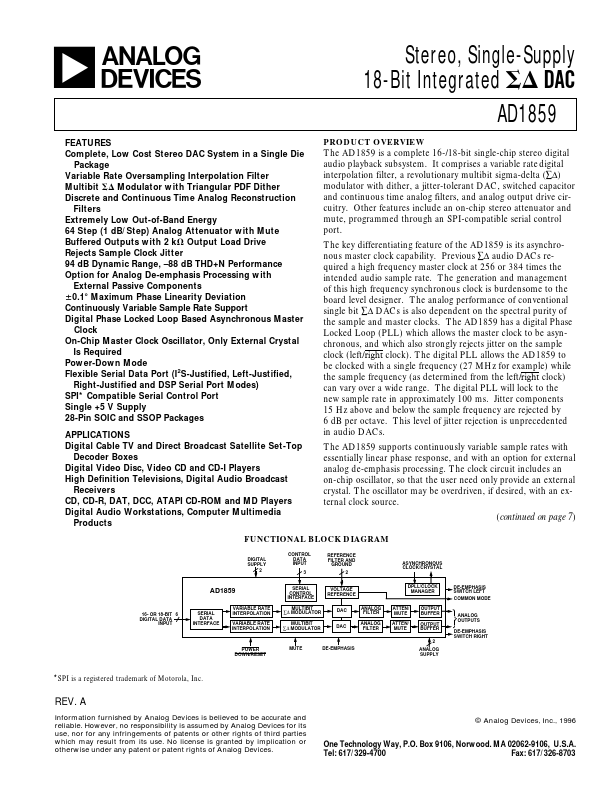

AD1859

Key Features

- The key differentiating feature of the AD1859 is its asynchronous master clock capability

- Previous ∑∆ audio DACs required a high frequency master clock at 256 or 384 times the intended audio sample rate

- The generation and management of this high frequency synchronous clock is burdensome to the board level designer

- The analog performance of conventional single bit ∑∆ DACs is also dependent on the spectral purity of the sample and master clocks

- The digital PLL will lock to the new sample rate in approximately 100 ms

- This level of jitter rejection is unprecedented in audio DACs

- The clock circuit includes an on-chip oscillator, so that the user need only provide an external crystal

- The oscillator may be overdriven, if desired, with an external clock source

- (continued on page 7)