AD9575 Description

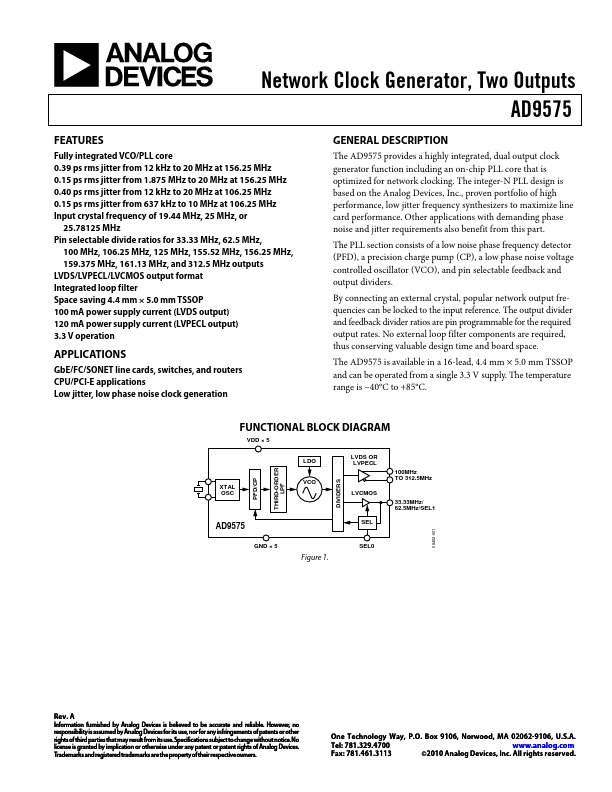

The AD9575 provides a highly integrated, dual output clock generator function including an on-chip PLL core that is optimized for network clocking. The integer-N PLL design is based on the Analog Devices, Inc., proven portfolio of high performance, low jitter frequency synthesizers to maximize line card performance. Other applications with demanding phase noise and jitter requirements also benefit from this part.