AD9625

FEATURES

12-bit 2.0 GSPS ADC, no missing codes SFDR = 80 d Bc, AIN up to 1 GHz at

- 1 d BFS, 2.0 GSPS SFDR = 76 d Bc, AIN up to 1.8 GHz at

- 1 d BFS, 2.0 GSPS SNR = 59 d BFS, AIN up to 1 GHz at

- 1 d BFS, 2.0 GSPS SNR = 58 d BFS, AIN up to 1.8 GHz at

- 1 d BFS, 2.0 GSPS Noise floor =

- 149.5 d BFS/Hz at 2.0 GSPS Power consumption: 3.5 W at 2.0 GSPS Differential analog input: 1.1 V p-p Differential clock input High speed 6- or 8-lane JESD204B serial output Subclass 1: 5.0 Gbps at 2.0 GSPS Two independent decimate by 8 or decimate by 16 filters with 10-bit NCOs Supply voltages: 1.3 V, 2.5 V Serial port control Flexible digital output modes Built-in selectable digital test patterns

12-Bit, 2.0 GSPS, 1.3 V/2.5 V Analog-to-Digital Converter AD9625

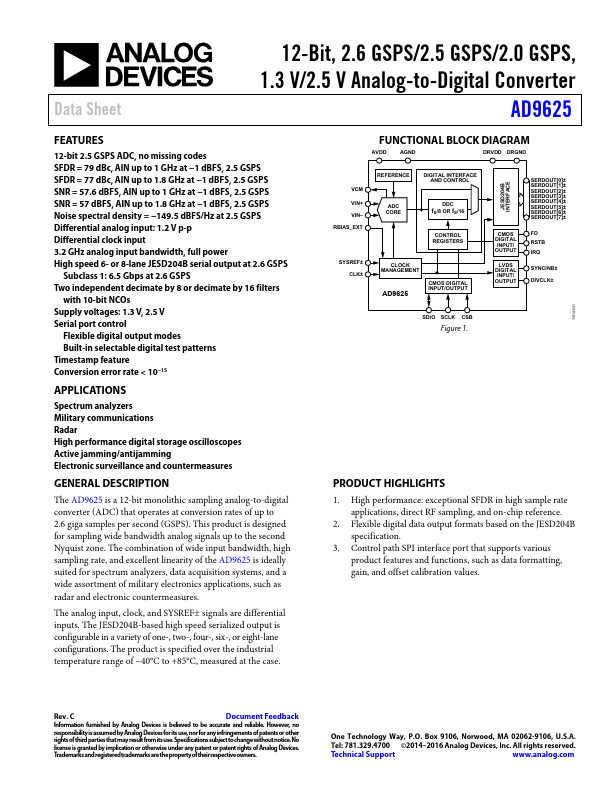

FUNCTIONAL BLOCK DIAGRAM

AVDD

AGND

DRVDD DRGND

REFERENCE

DIGITAL INTERFACE AND CONTROL

JESD204B INTERFACE

VIN+

VIN-

RBIAS

ADC CORE

DDC f S/8 OR f S/16

SERDOUT[0]± SERDOUT[1]± SERDOUT[2]± SERDOUT[3]± SERDOUT[4]± SERDOUT[5]± SERDOUT[6]±...