AD9882A Overview

Key Specifications

Package: LQFP

Mount Type: Surface Mount

Pins: 100

Operating Voltage: 3.3 V

Description

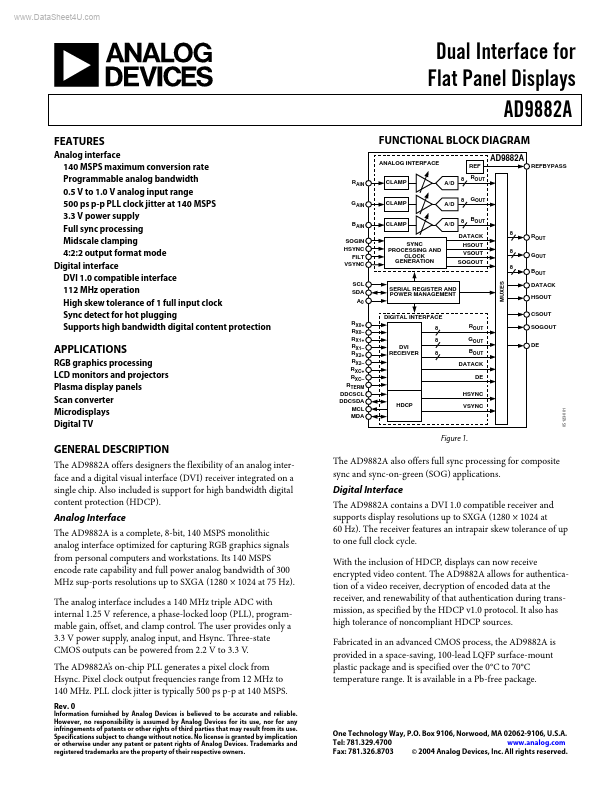

The AD9882A offers designers the flexibility of an analog interface and a digital visual interface (DVI) receiver integrated on a single chip. Also included is support for high bandwidth digital content protection (HDCP).