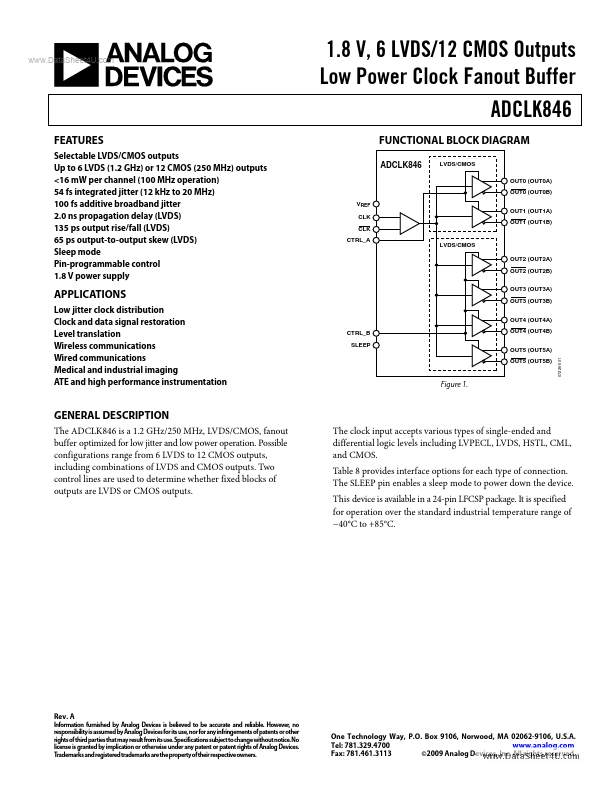

ADCLK846 Description

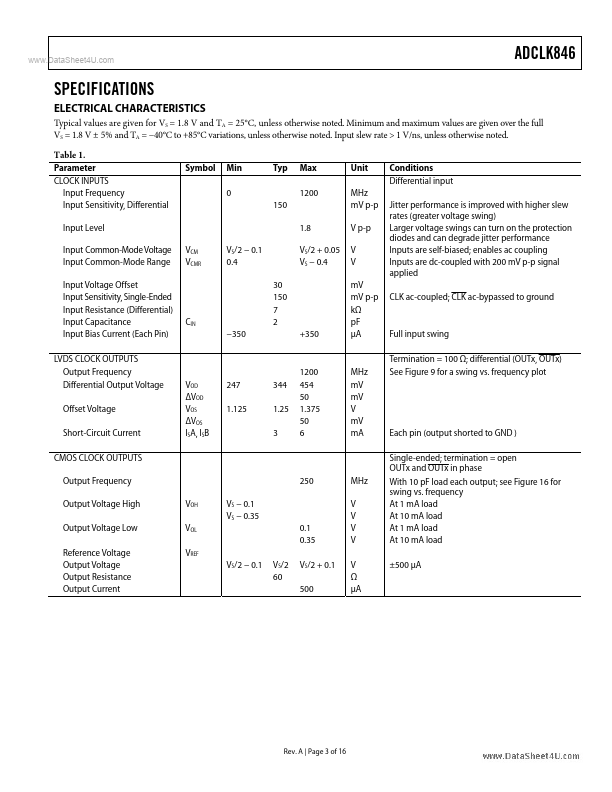

The ADCLK846 is a 1.2 GHz/250 MHz, LVDS/CMOS, fanout buffer optimized for low jitter and low power operation. Possible configurations range from 6 LVDS to 12 CMOS outputs, including binations of LVDS and CMOS outputs. Two control lines are used to determine whether fixed blocks of outputs are LVDS or CMOS outputs.