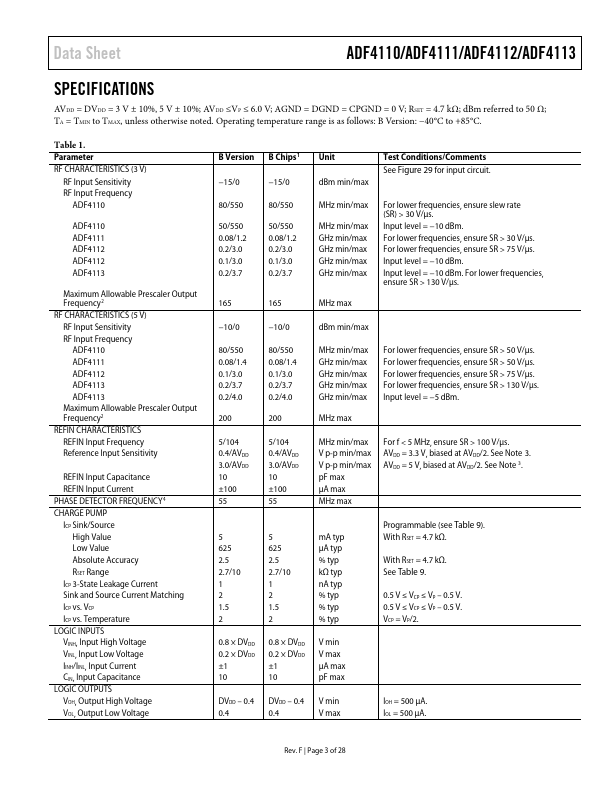

Datasheet Summary

Data Sheet

RF PLL Frequency Synthesizers ADF4110/ADF4111/ADF4112/ADF4113

Features

GENERAL DESCRIPTION

ADF4110: 550 MHz; ADF4111: 1.2 GHz; ADF4112: 3.0 GHz; ADF4113: 4.0 GHz

2.7 V to 5.5 V power supply

Separate charge pump supply (VP) allows extended tuning voltage in 3 V systems

Programmable dual-modulus prescaler 8/9, 16/17, 32/33, 64/65

The ADF4110 family of frequency synthesizers can be used to implement local oscillators in the upconversion and downconversion sections of wireless receivers and transmitters. They consist of a low noise digital PFD (phase frequency detector), a precision charge pump, a programmable reference divider, programmable A and B counters, and a dual-modulus...