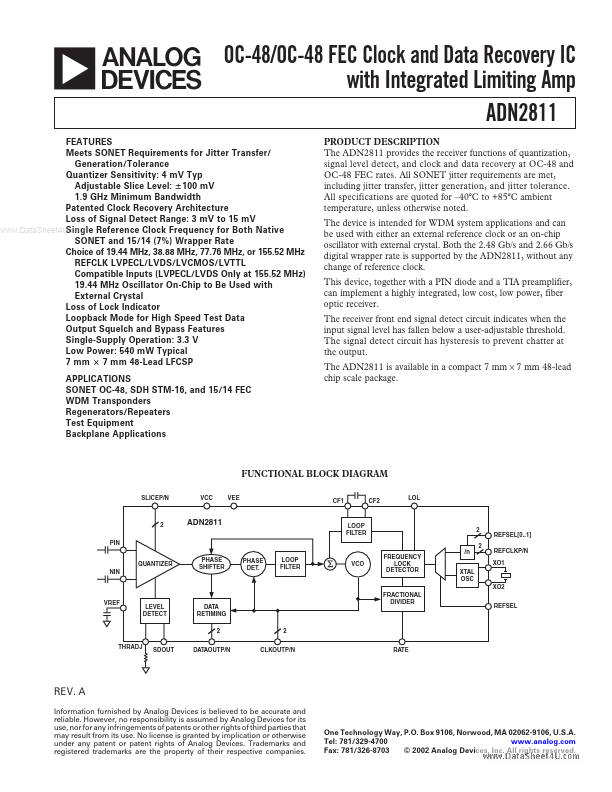

ADN2811 Overview

Key Features

- All SONET jitter requirements are met, including jitter transfer, jitter generation, and jitter tolerance

- All specifications are quoted for –40؇C to +85؇C ambient temperature, unless otherwise noted

- Both the 2.48 Gb/s and 2.66 Gb/s digital wrapper rate is supported by the ADN2811, without any change of reference clock

- This device, together with a PIN diode and a TIA preamplifier, can implement a highly integrated, low cost, low power, fiber optic receiver

- The receiver front end signal detect circuit indicates when the input signal level has fallen below a user-adjustable threshold

- The signal detect circuit has hysteresis to prevent chatter at the output

- The ADN2811 is available in a compact 7 mm × 7 mm 48-lead chip