ADP320 Description

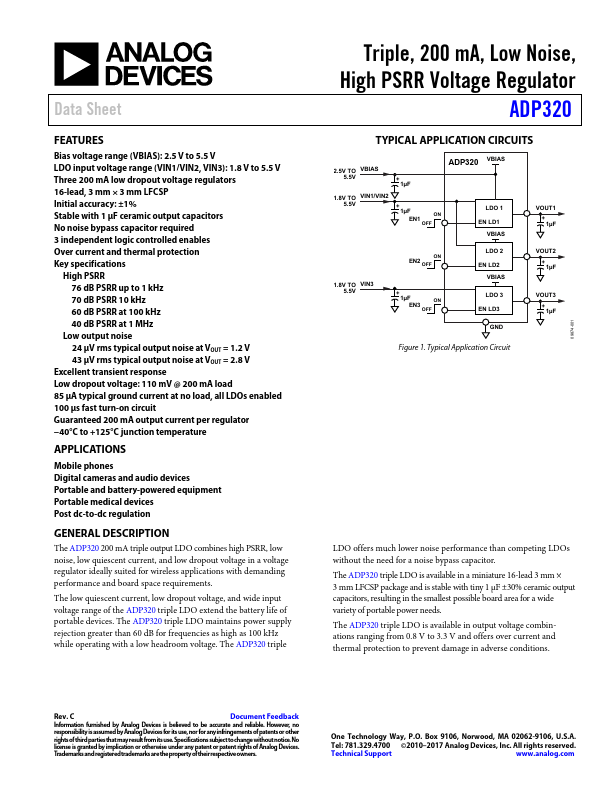

The ADP320 200 mA triple output LDO bines high PSRR, low noise, low quiescent current, and low dropout voltage in a voltage regulator ideally suited for wireless applications with demanding performance and board space requirements. The low quiescent current, low dropout voltage, and wide input voltage range of the ADP320 triple LDO extend the battery life of portable devices. The ADP320 triple LDO maintains power...