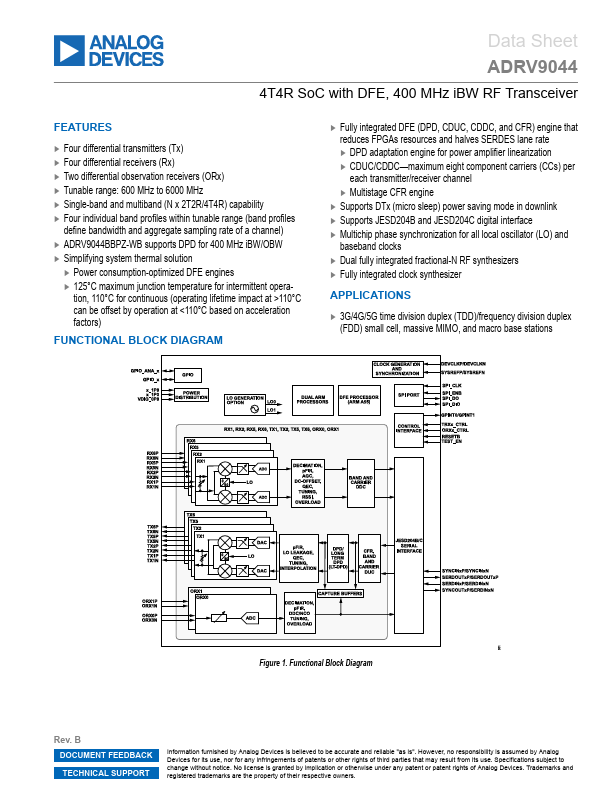

ADRV9044 Overview

Key Features

- Four differential transmitters (Tx)

- Four differential receivers (Rx)

- Two differential observation receivers (ORx)

- Tunable range: 600 MHz to 6000 MHz

- Four individual band profiles within tunable range (band profiles define bandwidth and aggregate sampling rate of a channel)