ADSP-BF536

ADSP-BF536 is Blackfin Embedded Processor manufactured by Analog Devices.

- Part of the ADSP-BF534 comparator family.

- Part of the ADSP-BF534 comparator family.

FEATURES

Blackfin® Embedded Processor ADSP-BF534/ADSP-BF536/ADSP-BF537

PERIPHERALS

IEEE 802.3-pliant 10/100 Ethernet MAC (ADSP-BF536 and ADSP-BF537 only) Controller area network (CAN) 2.0B interface Parallel peripheral interface (PPI), supporting ITU-R 656 video data formats Two dual-channel, full-duplex synchronous serial ports (SPORTs), supporting eight stereo I2S channels 12 peripheral DMAs, 2 mastered by the Ethernet MAC Two memory-to-memory DMAs with external request lines Event handler with 32 interrupt inputs Serial peripheral interface (SPI)-patible Two UARTs with Ir DA® support Two-wire interface (TWI) controller Eight 32-bit timer/counters with PWM support Real-time clock (RTC) and watchdog timer 32-bit core timer 48 general-purpose I/Os (GPIOs), 8 with high current drivers On-chip PLL capable of 1؋ to 63؋ frequency multiplication Debug/JTAG interface

Up to 600 MHz high performance Blackfin processor Two 16-bit MACs, two 40-bit ALUs, four 8-bit video ALUs, 40-bit shifter RISC-like register and instruction model for ease of programming and piler-friendly support Advanced debug, trace, and performance monitoring 0.8 V to 1.2 V core VDD with on-chip voltage regulation 2.5 V and 3.3 V-tolerant I/O with specific 5 V-tolerant pins 182-ball and 208-ball MBGA packages

MEMORY

Up to 132K bytes of on-chip memory prised of: Instruction SRAM/cache; instruction SRAM; data SRAM/cache; additional dedicated data SRAM; scratchpad SRAM (see Table 1 on Page 3 for available memory configurations) External memory controller with glueless support for SDRAM and asynchronous 8-bit and 16-bit memories Flexible booting options from external flash, SPI and TWI memory or from SPI, TWI, and UART host devices Memory management unit providing memory protection

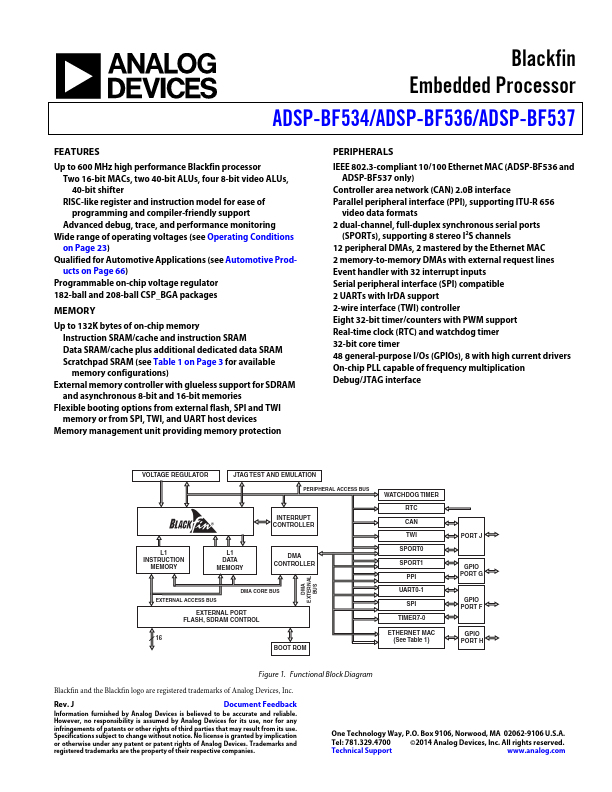

VOLTAGE REGULATOR

JTAG TEST AND EMULATION

PERIPHERAL ACCESS BUS

WATCHDOG TIMER

PERIPHERAL ACCESS BUS

L1 INSTRUCTION MEMORY

EXTERNAL ACCESS BUS

RTC CAN TWI SPORT0 SPORT1 GPIO PORT G PORT J

INTERRUPT CONTROLLER

L1 DATA...