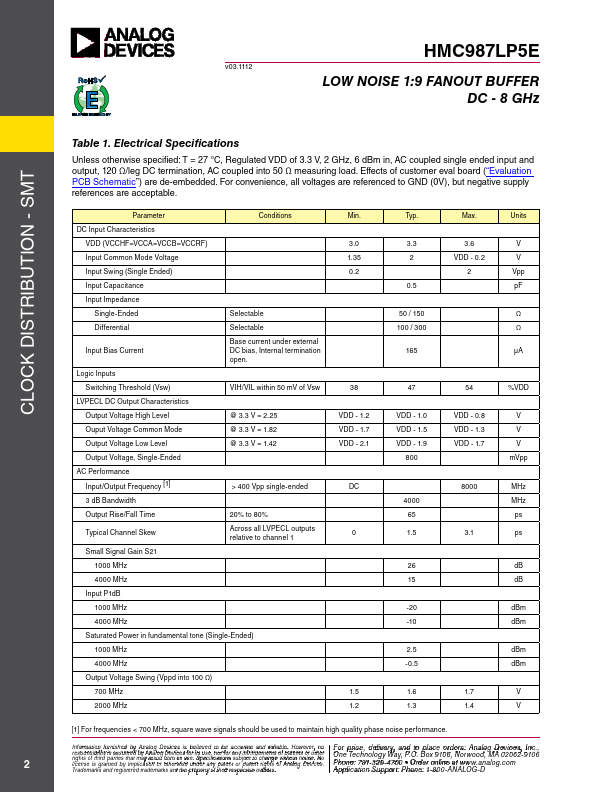

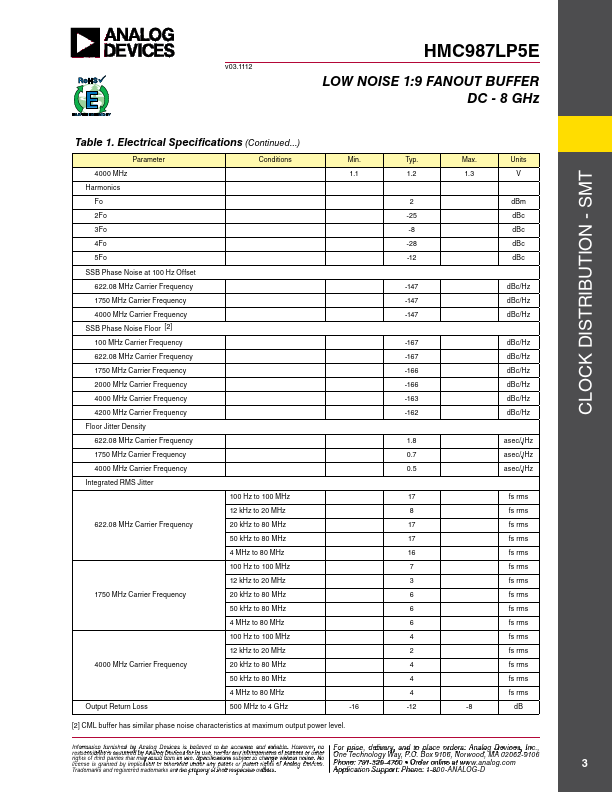

HMC987LP5E Description

The 1-to-9 fanout buffer is designed for low noise clock distribution. It is intended to generate relatively square wave outputs with rise/fall times < 100 ps. The low skew and jitter outputs of the HMC987LP5E, bined with its fast rise/fall times, leads to controllable low-noise switching of downstream circuits such as mixers, ADCs/DACs or SERDES devices.

HMC987LP5E Key Features

- 8 GHz Operating Frequency Flexible Input Interface

- 9 to 3 dBm Single-Ended Serial or Parallel Control, Hardware Chip-Enable Power-Down Current < 1 uA 32 Lead 5x5 mm SMT Pa