ATC35 Key Features

- prehensive Library of Standard Logic Cells

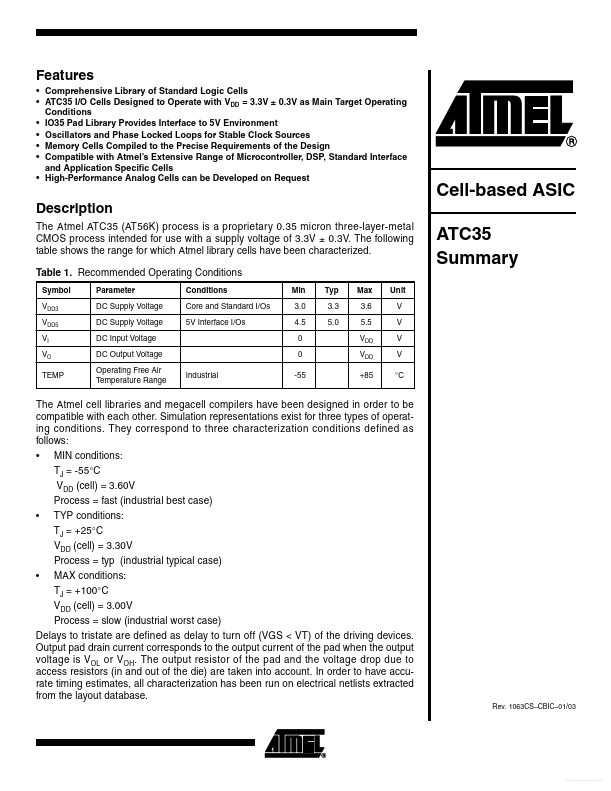

- ATC35 I/O Cells Designed to Operate with VDD = 3.3V ± 0.3V as Main Target Operating

- High-Performance Analog Cells can be Developed on Request

- MIN conditions: TJ = -55°C VDD (cell) = 3.60V Process = fast (industrial best case)

- TYP conditions: TJ = +25°C VDD (cell) = 3.30V Process = typ (industrial typical case)

- MAX conditions: TJ = +100°C VDD (cell) = 3.00V Process = slow (industrial worst case) Delays to tristate are defined as

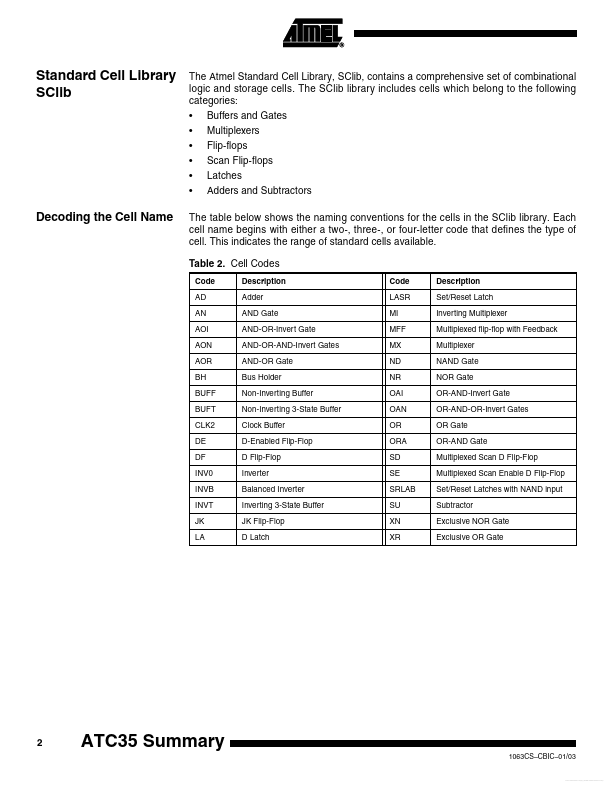

- Buffers and Gates Multiplexers Flip-flops Scan Flip-flops Latches Adders and Subtractors