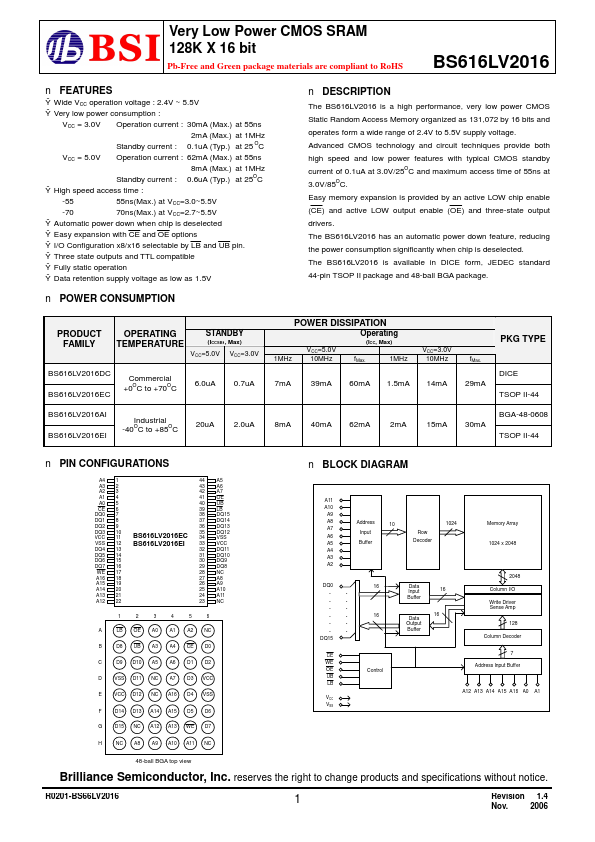

| Part | BS616LV2016 |

|---|---|

| Description | Very Low Power CMOS SRAM |

| Manufacturer | Brilliance Semiconductor |

| Size | 207.46 KB |

Pricing from 4.18 SGD, available from element14 APAC and Win Source.Powered by Octopart

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| element14 APAC | 0 | 1+ : 4.18 SGD 10+ : 3.72 SGD 25+ : 3.6 SGD 50+ : 3.56 SGD |

View Offer |

| Win Source | 1270 | 2+ : 41.0787 USD 4+ : 33.7064 USD 6+ : 32.653 USD 8+ : 31.5996 USD |

View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| LH52256C-10LL | Sharp Corporation | 256K SRAM |

| HM628512 | Hitachi Semiconductor | 4 M SRAM (512-kword x 8-bit) |

| HY62256A | Hyundai | 32K x 8-Bit CMOS SRAM |