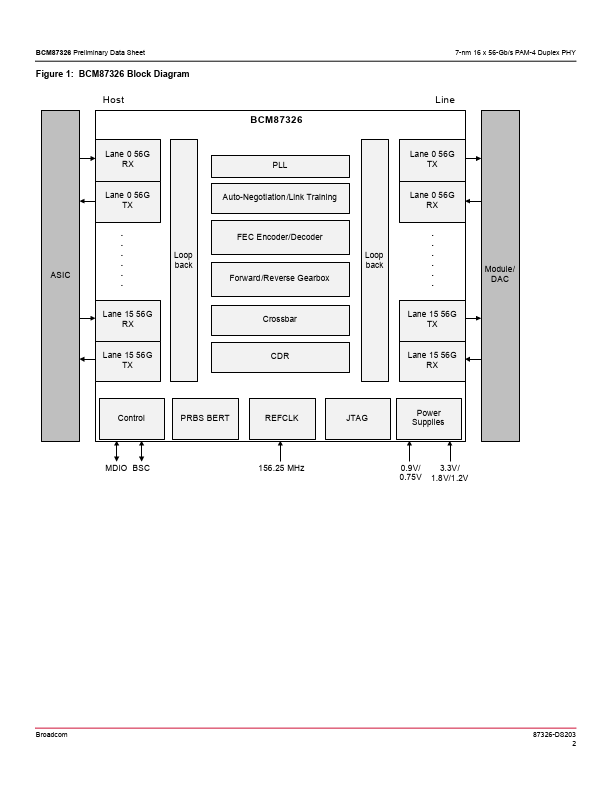

BCM87326 Description

.................................................................................................... 5 1.1 Device Functions ......................................................................................................................................................6 1.2 High-Speed Transmitter...

BCM87326 Key Features

- Host-side interface

- Long reach (LR): ~30 dB

- Line-side interface

- Chip-to-module (C2M) pliant

- Retimer, Forward, and Reverse Gearbox modes

- Flexible crossbar

- Supports forward error correction (FEC)

- Supports Mux and Broadcasting modes

- Supports 400G-CR8 mode

- Integrated AC-coupling capacitors at host-side and

BCM87326 Applications

- ASIC-to-module interface 16 × 56-Gb/s front-panel and backplane applications