CH7011A

CH7011A is Chrontel CH7011 TV Output Device manufactured by Chrontel.

Chrontel CHRONTEL CHRONTEL CHRONTEL ..

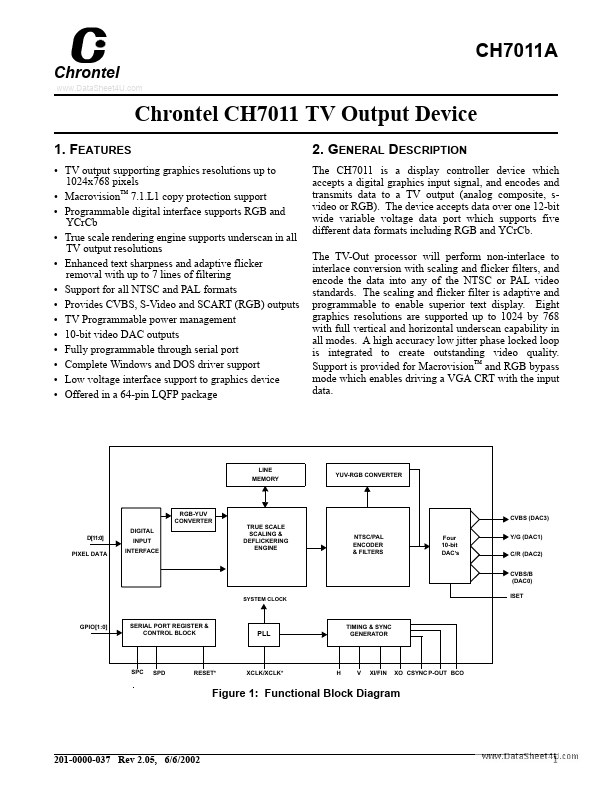

Chrontel CH7011 TV Output Device

1. Features

- TV output supporting graphics resolutions up to 1024x768 pixels

- Macrovision™ 7.1.L1 copy protection support

- Programmable digital interface supports RGB and YCrCb

- True scale rendering engine supports underscan in all TV output resolutions

- Enhanced text sharpness and adaptive flicker removal with up to 7 lines of filtering

- Support for all NTSC and PAL formats

- Provides CVBS, S-Video and SCART (RGB) outputs

- TV Programmable power management

- 10-bit video DAC outputs

- Fully programmable through serial port

- plete Windows and DOS driver support

- Low voltage...