CS4412A

Overview

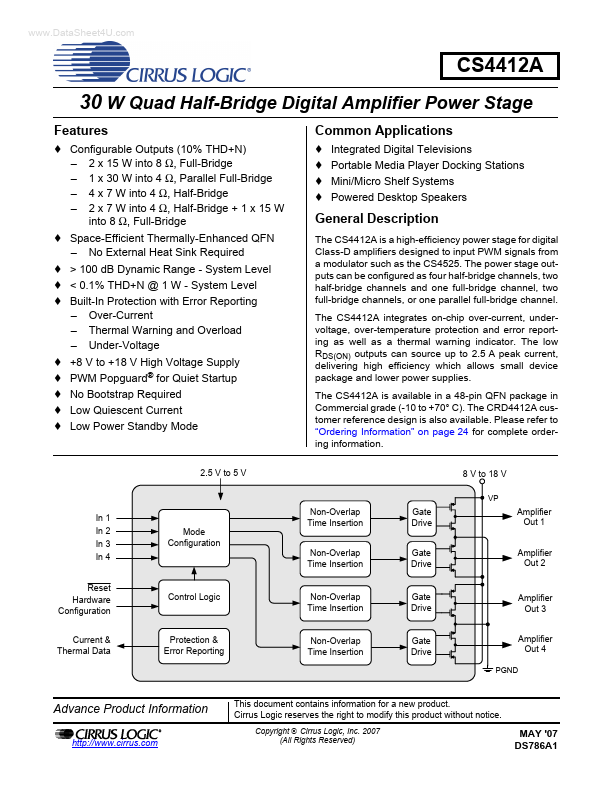

The CS4412A is a high-efficiency power stage for digital Class-D amplifiers designed to input PWM signals from a modulator such as the CS4525. The power stage outputs can be configured as four half-bridge channels, two half-bridge channels and one full-bridge channel, two full-bridge channels, or one parallel full-bridge channel.