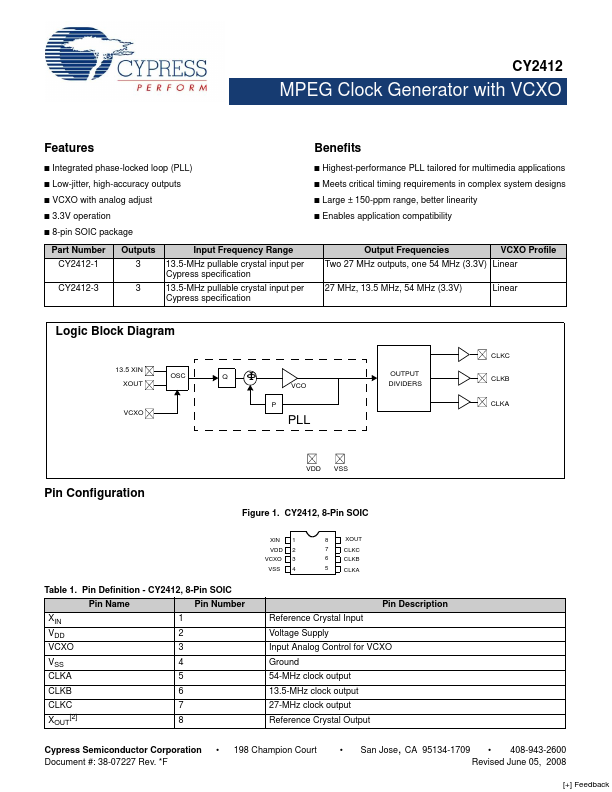

CY2412 Overview

CY2412 MPEG Clock Generator with VCXO.

CY2412 Key Features

- Integrated phase-locked loop (PLL)

- Low-jitter, high-accuracy outputs

- VCXO with analog adjust

- 3.3V operation

- 8-pin SOIC package

- Highest-performance PLL tailored for multimedia

CY2412 Applications

- Meets critical timing requirements in plex system designs