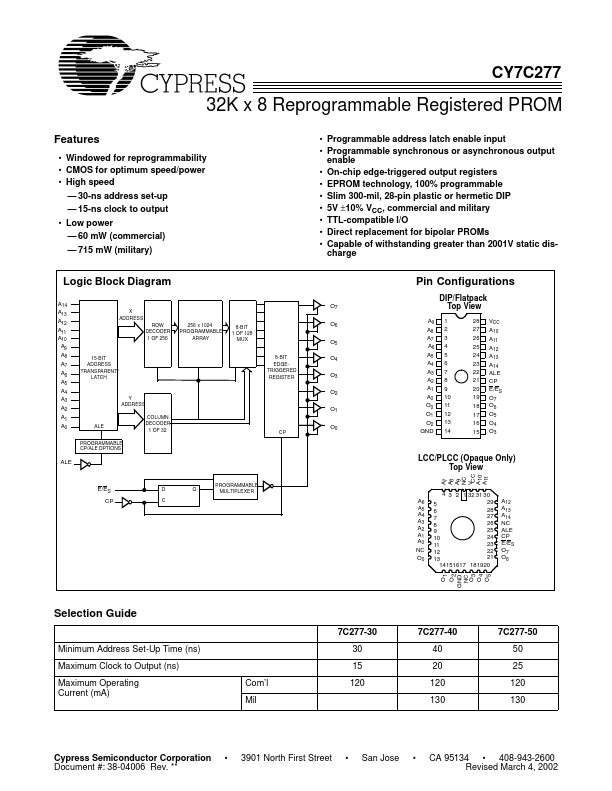

CY7C277 Description

77 CY7C277 32K x 8 Reprogrammable Registered PROM.

CY7C277 Key Features

- Windowed for reprogrammability

- CMOS for optimum speed/power

- High speed

- 30-ns address set-up

- 15-ns clock to output

- Low power

- 60 mW (mercial)

- 715 mW (military)

- Programmable address latch enable input

- Programmable synchronous or asynchronous output enable