CY7C342B Description

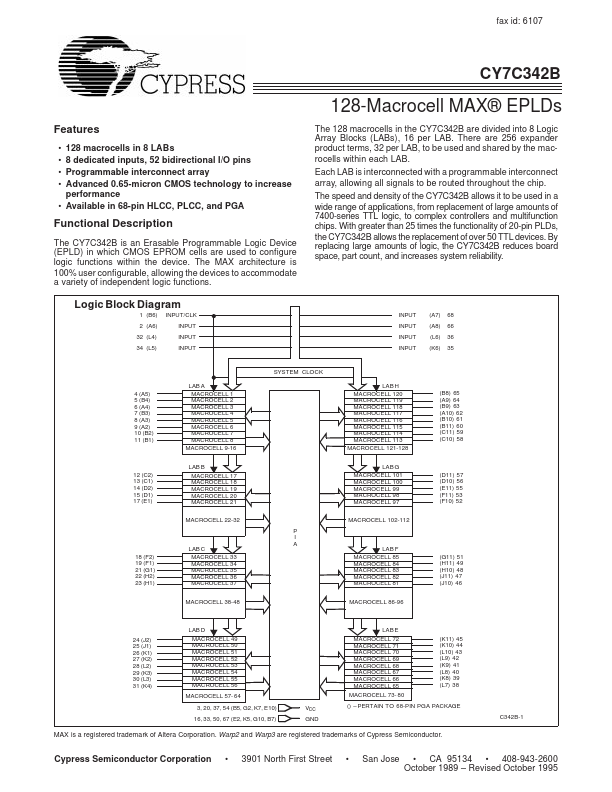

The CY7C342B is an Erasable Programmable Logic Device (EPLD) in which CMOS EPROM cells are used to configure logic functions within the device. The MAX architecture is 100% user configurable, allowing the devices to acmodate a variety of independent logic functions. There are 256 expander product terms, 32 per LAB, to be used and shared by the macrocells within each LAB.

CY7C342B Key Features

- 128 macrocells in 8 LABs

- 8 dedicated inputs, 52 bidirectional I/O pins

- Programmable interconnect array

- Advanced 0.65-micron CMOS technology to increase

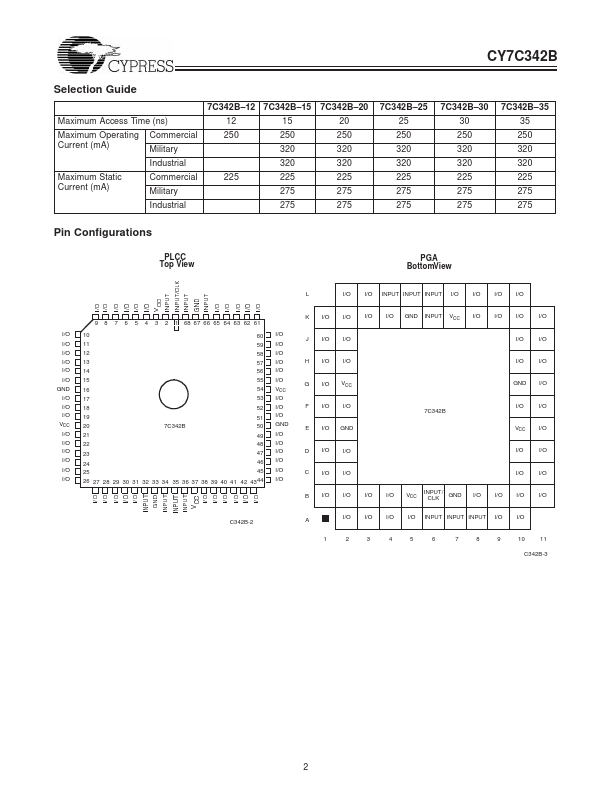

- Available in 68-pin HLCC, PLCC, and PGA