CY14B101NA

Overview

- 20 ns, 25 ns, and 45 ns access times

- Internally organized as 128 K × 8 (CY14B101LA) or 64 K × 16 (CY14B101NA)

- Hands off automatic STORE on power-down with only a small capacitor

- STORE to QuantumTrap nonvolatile elements initiated by software, device pin, or AutoStore on power-down

- RECALL to SRAM initiated by software or power-up

- Infinite read, write, and RECALL cycles

- 1 million STORE cycles to QuantumTrap

- 20 year data retention

- Single 3 V +20% to -10% operation

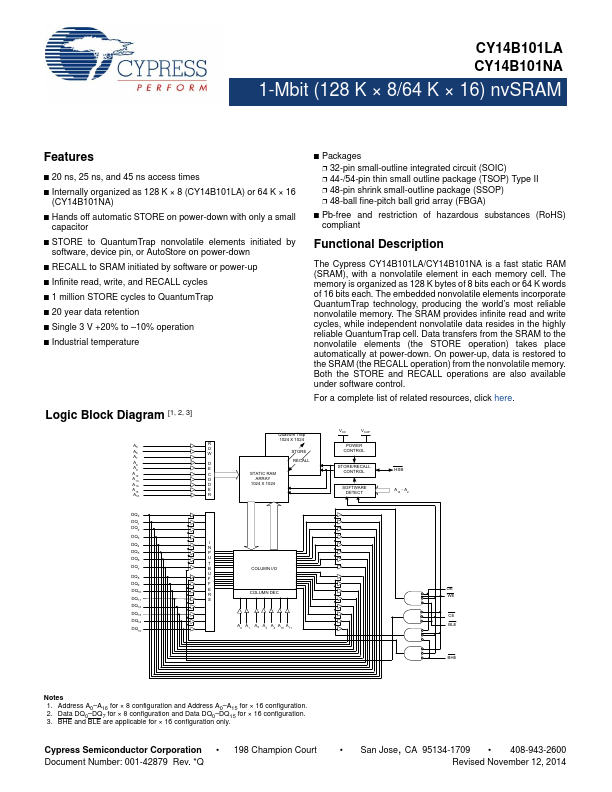

- Industrial temperature Logic Block Diagram [1, 2, 3]