CY14B512P

Features

- -

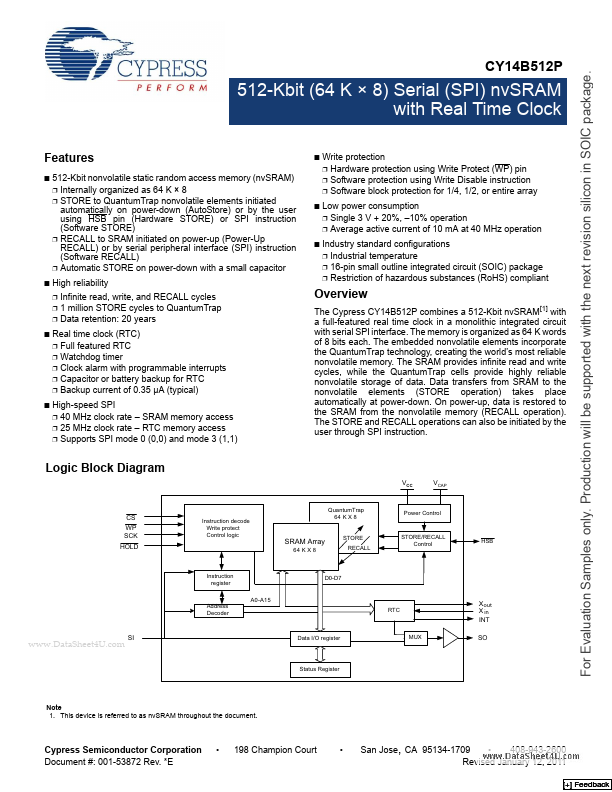

512-Kbit nonvolatile static random access memory (nv SRAM)

- Internally organized as 64 K × 8

- STORE to Quantum Trap nonvolatile elements initiated automatically on power-down (Auto Store) or by the user using HSB pin (Hardware STORE) or SPI instruction (Software STORE)

- RECALL to SRAM initiated on power-up (Power-Up RECALL) or by serial peripheral interface (SPI) instruction (Software RECALL)

- Automatic STORE on power-down with a small capacitor High reliability

- -

- Write protection

- Hardware protection using Write Protect (WP) pin

- Software protection using Write Disable instruction

- Software block protection for 1/4, 1/2, or entire array Low power consumption

- Single 3 V + 20%,

- 10% operation

- Average active current of 10 m A at 40 MHz operation Industry standard configurations

- Industrial temperature

- 16-pin small outline integrated circuit (SOIC) package

- Restriction of hazardous substances (Ro HS) pliant

- -

- Infinite read, write, and RECALL cycles 1...