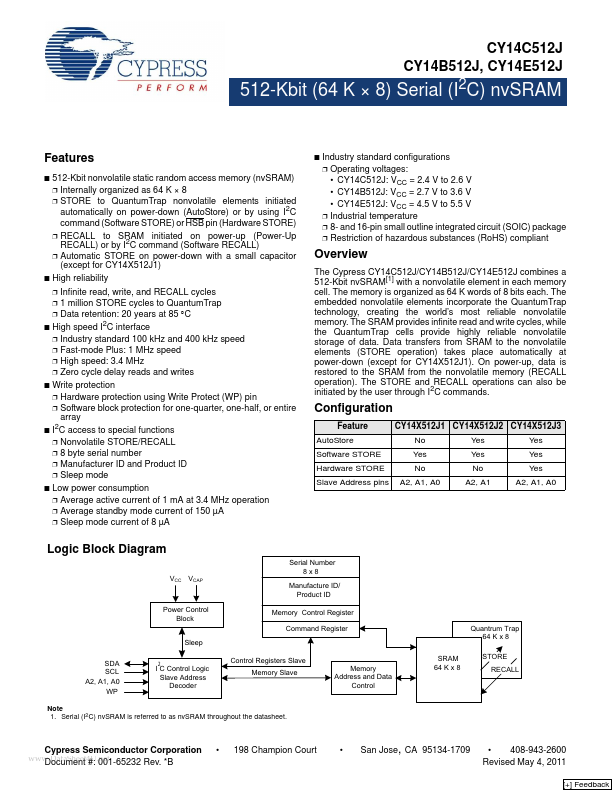

CY14C512J

Overview

- 512-Kbit nonvolatile static random access memory (nvSRAM) ❐ Internally organized as 64 K × 8 ❐ STORE to QuantumTrap nonvolatile elements initiated automatically on power-down (AutoStore) or by using I2C command (Software STORE) or HSB pin (Hardware STORE) ❐ RECALL to SRAM initiated on power-up (Power-Up RECALL) or by I2C command (Software RECALL) ❐ Automatic STORE on power-down with a small capacitor (except for CY14X512J1)

- High reliability Infinite read, write, and RECALL cycles 1 million STORE cycles to QuantumTrap ❐ Data retention: 20 years at 85 °C 2

- High speed I C interface ❐ Industry standard 100 kHz and 400 kHz speed ❐ Fast-mode Plus: 1 MHz speed ❐ High speed: 3.4 MHz ❐ Zero cycle delay reads and writes

- Write protection ❐ Hardware protection using Write Protect (WP) pin ❐ Software block protection for one-quarter, one-half, or entire array 2

- I C access to special functions ❐ Nonvolatile STORE/RECALL ❐ 8 byte serial number ❐ Manufacturer ID and Product ID ❐ Sleep mode

- Low power consumption ❐ Average active current of 1 mA at 3.4 MHz operation ❐ Average standby mode current of 150 µA ❐ Sleep mode current of 8 µA ❐ ❐ Industry standard configurations ❐ Operating voltages:

- CY14C512J: VCC = 2.4 V to 2.6 V

- CY14B512J: VCC = 2.7 V to 3.6 V

- CY14E512J: VCC = 4.5 V to 5.5 V ❐ Industrial temperature ❐ 8- and 16-pin small outline integrated circuit (SOIC) package ❐ Restriction of hazardous substances (RoHS) compliant Overview The Cypress CY14C512J/CY14B512J/CY14E512J combines a 512-Kbit nvSRAM[1] with a nonvolatile element in each memory cell. The memory is organized as 64 K words of 8 bits each. The embedded nonvolatile elements incorporate the QuantumTrap technology, creating the world’s most reliable nonvolatile memory. The SRAM provides infinite re