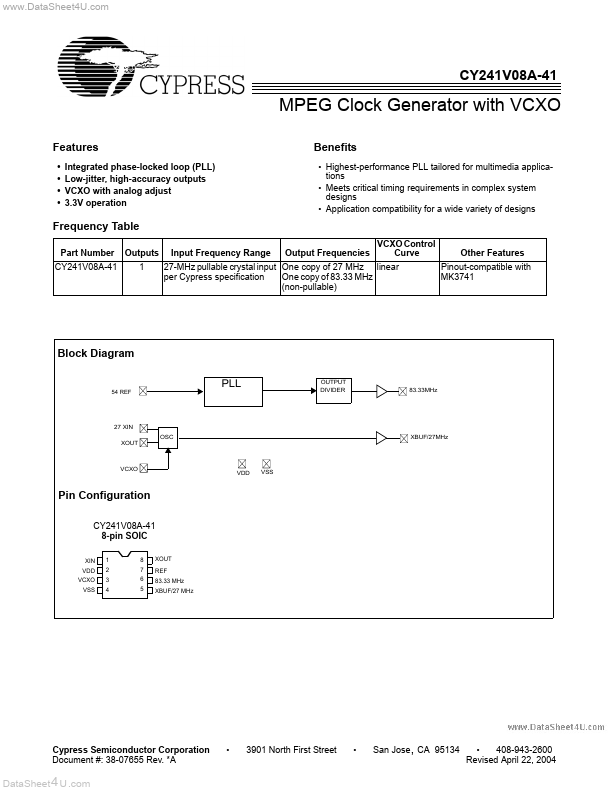

CY241V08A-41 Overview

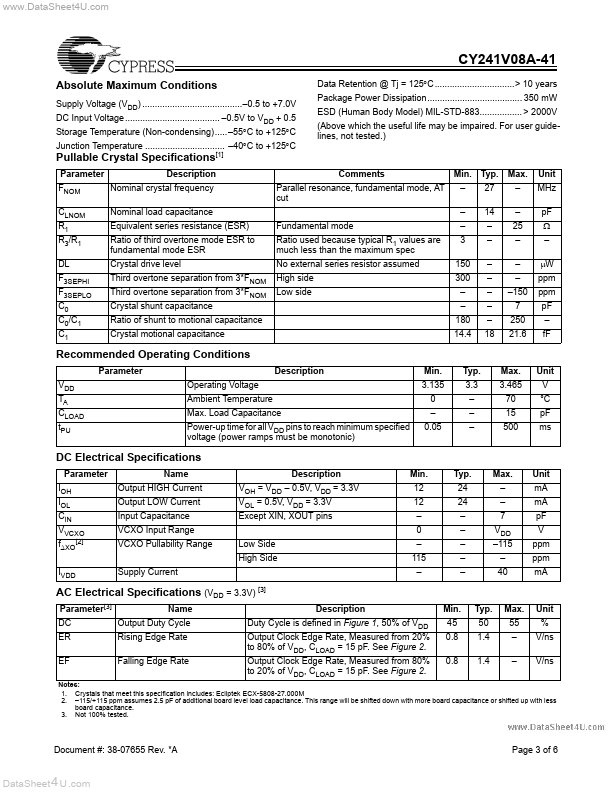

A Page 2 of 6 DataSheet 4 U . CY241V08A-41 Conditions Supply Voltage (VDD) ........................................ 0.5 to +7.0V DC Input Voltage......................................

CY241V08A-41 Key Features

- Integrated phase-locked loop (PLL) Low-jitter, high-accuracy outputs VCXO with analog adjust 3.3V operation

- Highest-performance PLL tailored for multimedia

CY241V08A-41 Applications

- Meets critical timing requirements in plex system designs

- Application patibility for a wide variety of designs