CY26049-36

Overview

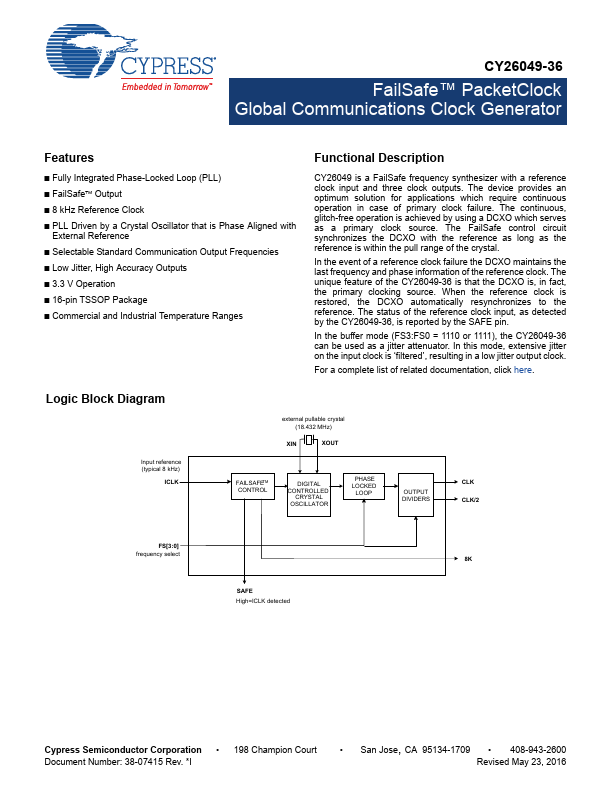

- Fully integrated phase-locked loop (PLL)

- FailSafe output

- PLL driven by a crystal oscillator that is phase aligned with external reference

- Output frequencies selectable and/or programmed to standard communication frequencies

- Low-jitter, high-accuracy outputs

- Commercial and Industrial operation

- 3.3V ± 5% operation

- 16-lead TSSOP

- When reference is in range, SAFE pin is driven high.

- When reference is off, DCXO maintains clock outputs. SAFE pin is low.