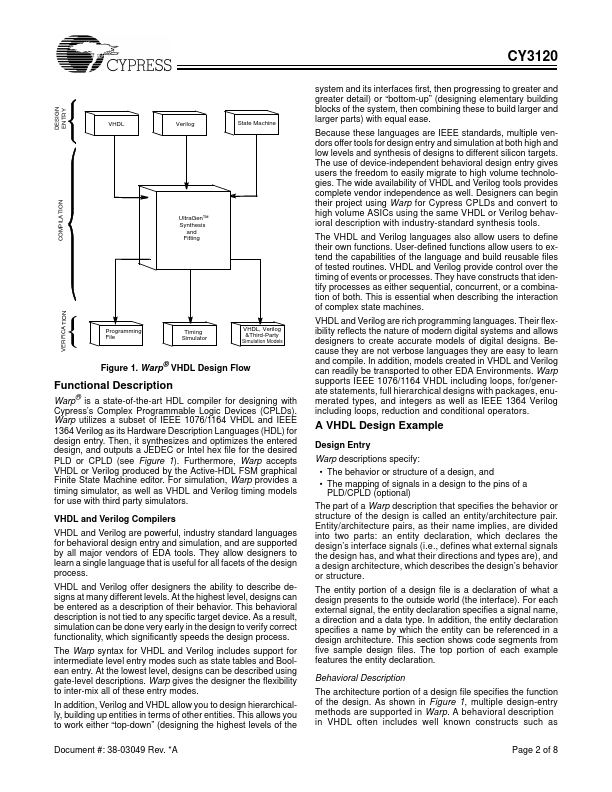

CY3120 Description

0.

CY3120 Key Features

- VHDL (IEEE 1076 and 1164) and Verilog (IEEE 1364) high-level language pilers with the following features

- Designs are portable across multiple devices and/or EDA environments

- Facilitates the use of industry-standard simulation and synthesis tools for board and system-level design

- User selectable speed and/or area optimization on a block-by-block basis

- Perfect munication between synthesis and fitting

- Automatic selection of optimal flip-flop type (D type/T type)

- Automatic pin assignment

- Supports all Cypress Programmable Logic Devices

- PSI™ (Programmable Serial Interface)

- Delta39K™ CPLDs