CY3125 Description

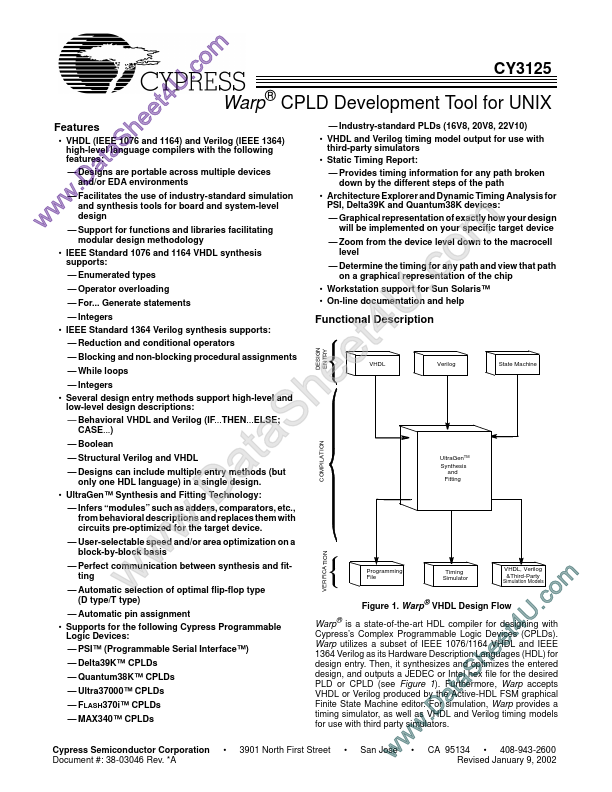

VHDL Verilog PILATION UltraGenTM Synthesis and Fitting VERFICA TION Programming File Timing Simulator Industry-standard PLDs (16V8, 20V8, 22V10) VHDL and Verilog timing model output for use with third-party simulators Static Timing Report: Provides timing information for any path broken down by the different steps of the path Architecture Explorer and Dynamic Timing Analysis for PSI, Delta39K and Quantum38K devices:...

CY3125 Key Features

- VHDL (IEEE 1076 and 1164) and Verilog (IEEE 1364) high-level language pilers with the following features

- Designs are portable across multiple devices and/or EDA environments

- Facilitates the use of industry-standard simulation and synthesis tools for board and system-level design

- Support for functions and libraries facilitating modular design methodology

- IEEE Standard 1076 and 1164 VHDL synthesis supports

- Enumerated types

- Operator overloading

- For... Generate statements

- Blocking and non-blocking procedural assignments

- While loops