CY7C1012AV33

Overview

- High speed - tAA = 8, 10, 12 ns

- Low active power - 1080 mW (max.)

- Operating voltages of 3.3 ± 0.3V

- 2.0V data retention

- Automatic power-down when deselected

- TTL-compatible inputs and outputs

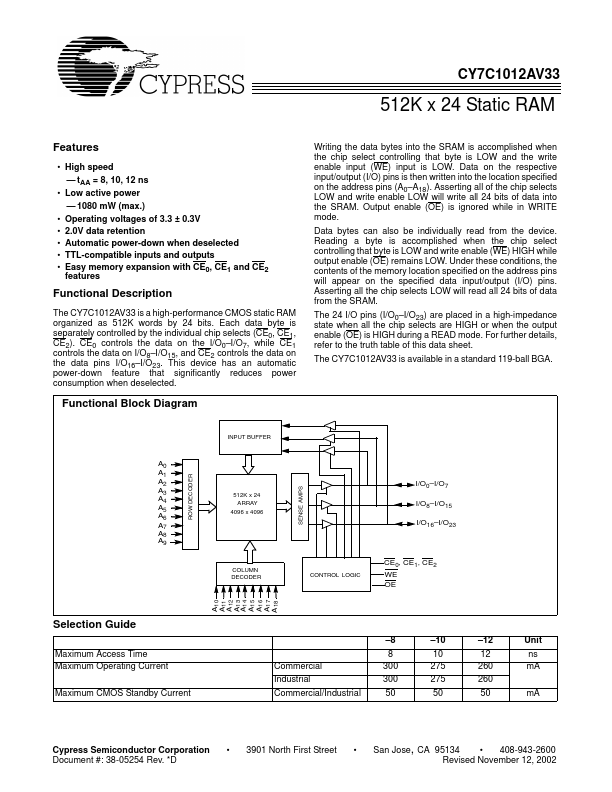

- Easy memory expansion with CE0, CE1 and CE2 features Writing the data bytes into the SRAM is accomplished when the chip select controlling that byte is LOW and the write enable input (WE) input is LOW. Data on the respective input/output (I/O) pins is then written into the location specified on the address pins (A0-A18). Asserting all of the chip selects LOW and write enable LOW will write all 24 bits of data into the SRAM. Output enable (OE) is ignored while in WRITE mode. Data bytes can also be individually read from the device. Reading a byte is accomplished when the chip select controlling that byte is LOW and write enable (WE) HIGH while output enable (OE) remains LOW. Under these conditions, the contents of the memory location specified on the address pins will appear on the specified data input/output (I/O) pins. Asserting all the chip selects LOW will read all 24 bits of data from the SRAM. The 24 I/O pins (I/O0-I/O23) are placed in a high-impedance state when all the chip selects are HIGH or when the output enable (OE) is HIGH during a READ mode. For further details, refer to the truth table of this data sheet. The CY7C1012AV33 is available in a standard 119-ball BGA. Functional Description The CY7C1012AV33 is a high-performance CMOS static RAM organized as 512K words by 24 bits. Each data byte is separately controlled by the individual chip selects (CE0, CE1, CE2). CE0 controls the data on the I/O0-I/O7, while CE1 controls the data on I/O8-I/O15, and CE2 controls the data on the data pins I/O16-I/O23. This device has an automatic power-down feature that significantly reduces power consumption when deselected. Functional Block Diagram