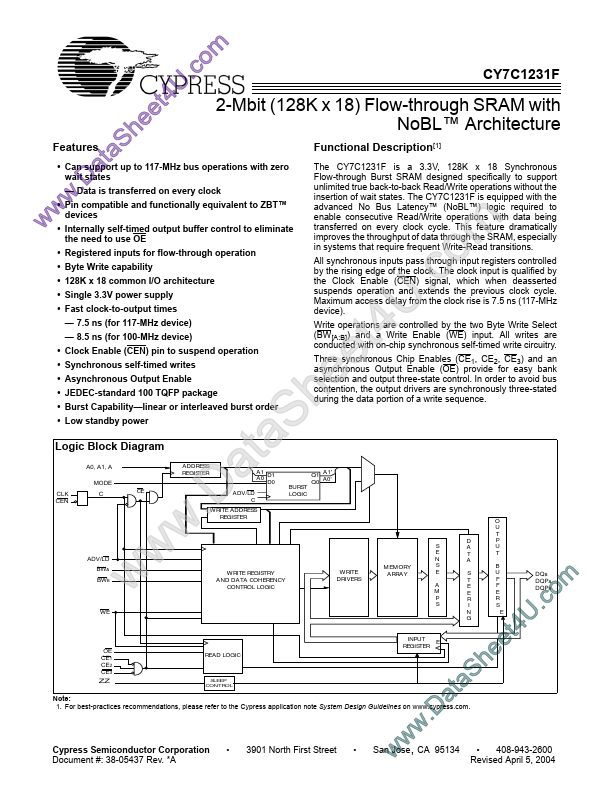

CY7C1231F Description

The CY7C1231F is equipped with the advanced No Bus Latency™ (NoBL™) logic required to enable consecutive Read/Write operations with data being transferred on every clock cycle.

CY7C1231F Key Features

- Can support up to 117-MHz bus operations with zero wait states

- Data is transferred on every clock

- Pin patible and functionally equivalent to ZBT™ devices

- Internally self-timed output buffer control to eliminate the need to use OE

- Registered inputs for flow-through operation

- Byte Write capability

- 128K x 18 mon I/O architecture

- Single 3.3V power supply

- Fast clock-to-output times

- 7.5 ns (for 117-MHz device)