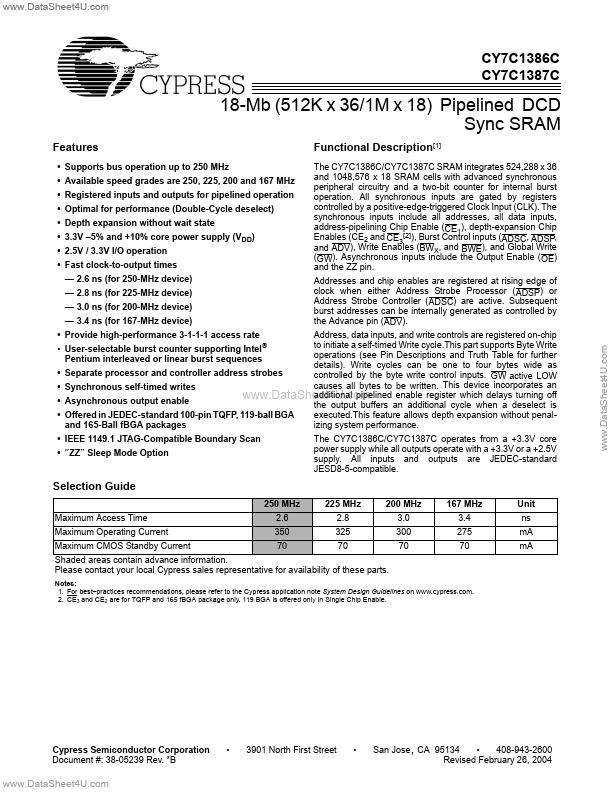

CY7C1386C Overview

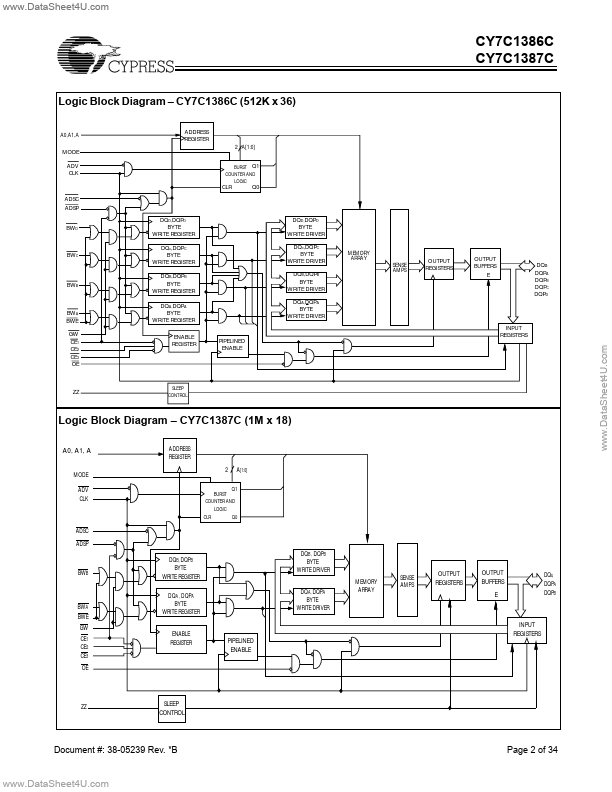

All synchronous inputs are gated by registers controlled by a positive-edge-triggered Clock Input (CLK). The synchronous inputs include all addresses, all data inputs, address-pipelining Chip Enable (CE1), depth-expansion Chip Enables (CE2 and CE3[2]), Burst Control inputs (ADSC, ADSP, and ADV), Write Enables (BWX, and BWE), and Global Write (GW). Asynchronous inputs include the Output Enable (OE) and the ZZ pin.

CY7C1386C Key Features

- Supports bus operation up to 250 MHz

- Available speed grades are 250, 225, 200 and 167 MHz

- Registered inputs and outputs for pipelined operation

- Optimal for performance (Double-Cycle deselect)

- Depth expansion without wait state

- 3.3V -5% and +10% core power supply (VDD)

- 2.5V / 3.3V I/O operation

- Fast clock-to-output times

- 2.6 ns (for 250-MHz device)

- 2.8 ns (for 225-MHz device)