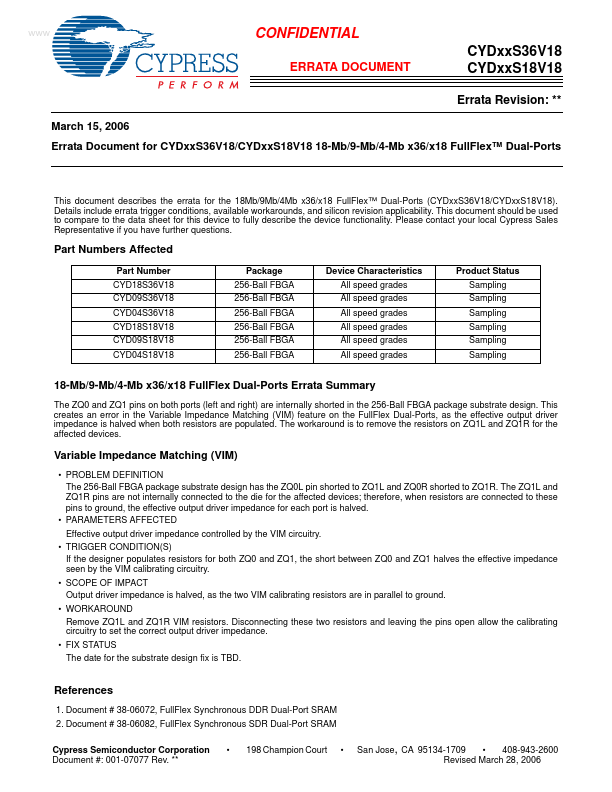

| Part | CYD04S36V18 |

|---|---|

| Description | V18) 18-Mb/9-Mb/4-Mb x36/x18 FullFlex Dual-Ports |

| Manufacturer | Cypress |

| Size | 72.46 KB |

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| No distributor offers were returned for this part. | |||

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| IP6538 | Injoinic | Dual ports Type-C Buck Converter |

| JMS561 | JMicron | SuperSpeed USB to Dual SATA Gen3 Ports Bridge |

| JMS562 | JMicron | SuperSpeed USB and eSATA Gen3 to Dual SATA Gen3 Ports Bridge |